# onsemi

## Highly Integrated Dual-Mode Active Clamp PWM Controller NCP1566

The NCP1566 is a highly integrated dual-mode active-clamp PWM controller targeting next-generation high-density, high-performance and small to medium power level isolated dc-dc converters for use in telecom and datacom industries. It can be configured in either voltage mode control with input voltage feed-forward or peak current mode control. Peak current mode control may be implemented with input voltage feedforward as well. Adjustable adaptive overlap time optimizes system efficiency based on input voltage and load conditions.

This controller integrates all the necessary control and protection functions to implement an isolated active clamp forward or asymmetric half-bridge converter. It integrates a high-voltage startup bias regulator. The NCP1566 has a line undervoltage detector, cycle-by-cycle current limiting, line voltage dependent maximum duty ratio limit, over voltage protection, and programmable overtemperature protection using an external thermistor. It also includes a dual-function FLT/SD pin used for communicating the presence of a fault but also for shutting down the controller. A dedicated dual-function synchronization pin eases operations when associating bricks together.

#### **General Features**

- Support Voltage Mode Control and Peak Current Mode Control

- Line Feedforward

- Adaptive Overlap time Control for Improved Efficiency

- Integrated 120–V High Voltage Startup Circuit with Self–Supply Operation

- Line Undervoltage Lockout (UVLO) with Adjustable Hysteresis

- Cycle by Cycle Peak Current Limiting

- Adjustable Over Power Protection

- Overcurrent Protection Based on Average Current

- Short Circuit Protection

- Programmable Maximum Duty Ratio Clamp

- Programmable Soft-Start

- External Over-temperature Protection Using a Thermistance

- Over Voltage Protection through a dedicated pin

- FLT/SD pin Used for Fault reporting and Shutdown Input

- Programmable Oscillator with a 1 MHz Maximum Frequency and Synchronization Capability

- 5 V/2% Voltage Reference

- Main Switch Drive Capability of -2 A / 3 A

- Active Clamp Switch Drive Capability of -2 A / 1 A

- V<sub>cc</sub> Range: from 6.5 V to 20 V

- This is a Pb and Halogen Free Device

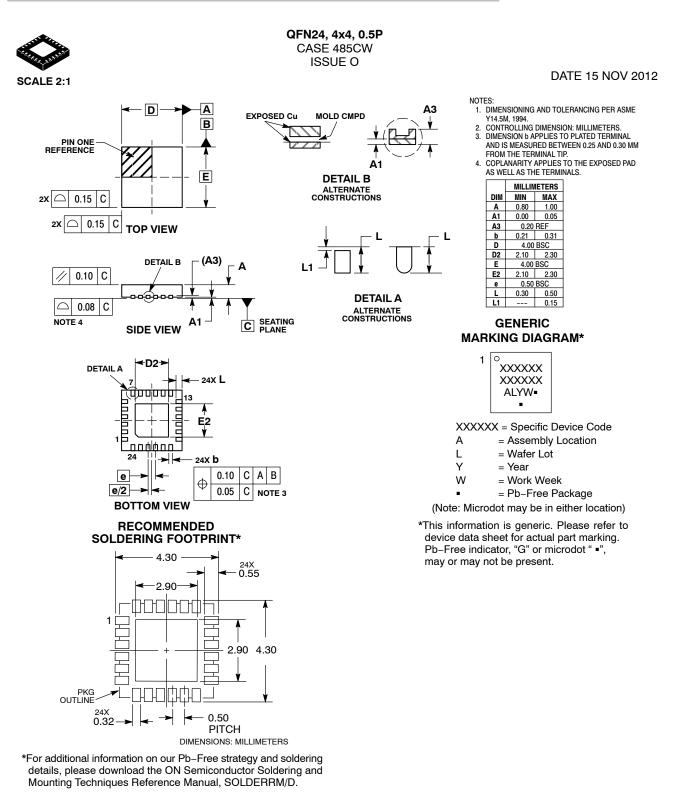

SCALE 2:1

QFN24, 4 x 4, 0.5P MTNTXG SUFFIX CASE 485CW

## MARKING DIAGRAM

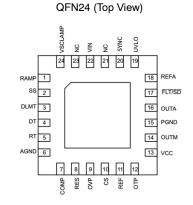

## **PIN CONNECTIONS**

#### **ORDERING INFORMATION**

See detailed ordering and shipping information on page 36 of this data sheet.

1

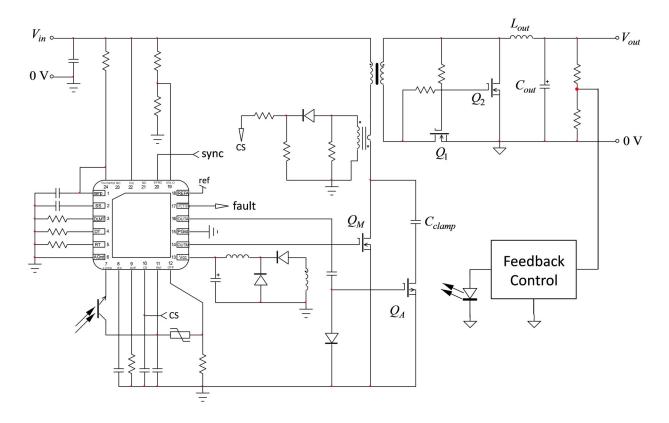

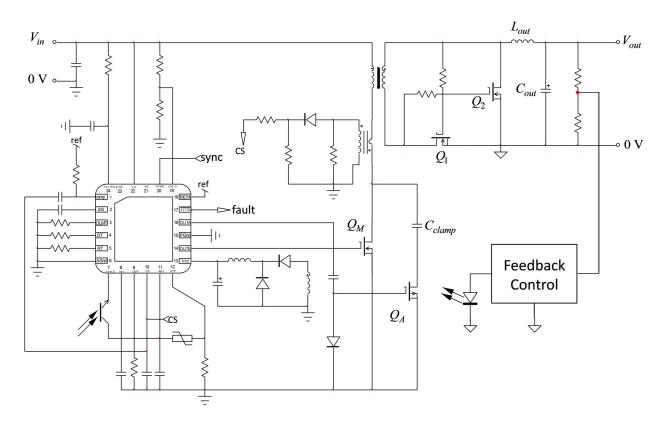

## **Typical Applications**

- High–Efficiency Isolated Dc–Dc Converters

- Server Power Supplies

- 24 V and 48 V Telecom Systems

- 42 V Automotive Applications

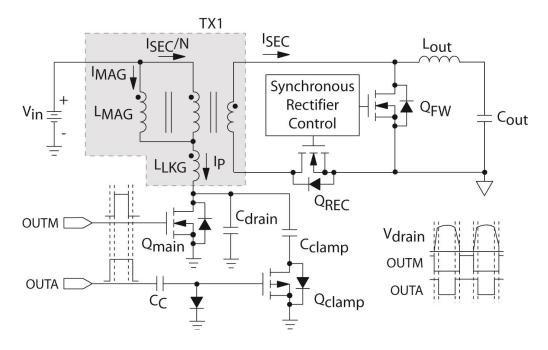

Figure 1. Typical Application Circuit in Voltage Mode Control

Figure 2. Typical Application Circuit in Current Mode Control

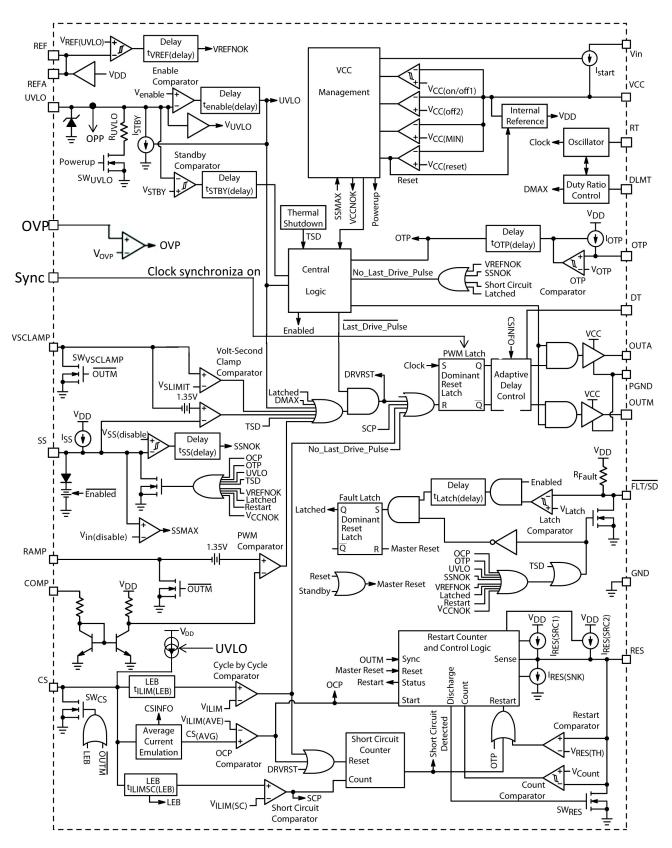

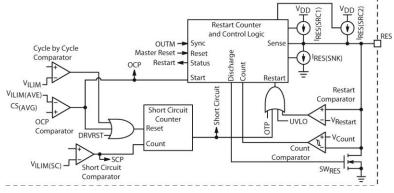

Figure 3. Functional Block Diagram

## Table 1. DETAILED PIN DESCRIPTION

| Pin Number | Name   | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

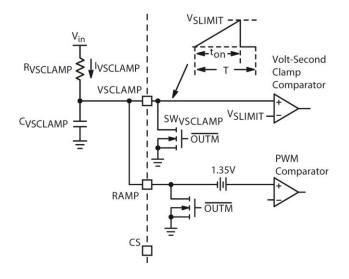

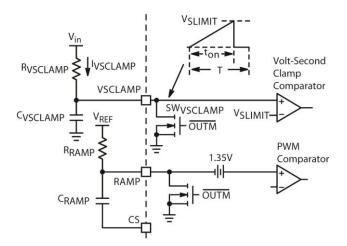

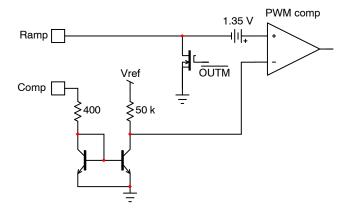

| 1          | RAMP   | PWM modulator ramp. In voltage mode an external R–C circuit from V <sub>in</sub> sets the PWM Ramp slope to implement feedforward. In current mode control, the resistor of the external R–C circuit connects to REF for ramp compensation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 2          | SS     | Soft-start control. A 20 $\mu$ A current source charges the external capacitor connected to this pin. Duty ratio is limited during startup by comparing the voltage on this pin to a level-shifted VSCLAMP signal. Under steady state conditions, the SS voltage is approximately 4.5 V. Once a fault is detected the SS capacitor is discharged and the controller is disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 3          | DLMT   | Maximum duty ratio limit. A resistor between this pin and AGND sets the maximum duty ratio of the controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

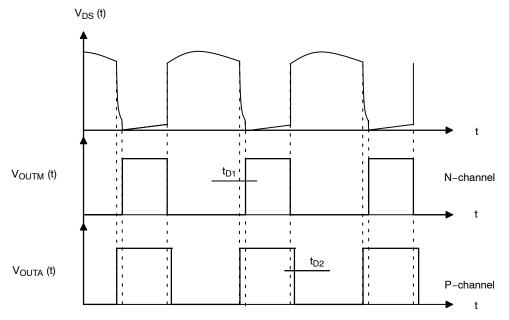

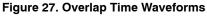

| 4          | DT     | Dead time control. An external resistor between this pin and AGND sets the overlap time delay between OUTM and OUTA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 5          | RT     | Oscillator frequency setting pin. The total external resistance connected between the RT and AGND pins sets the internal oscillator frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 6          | AGND   | Analog circuit ground reference. All control and timing components that connect to AGND should have the shortest loop possible to this pin to improve noise immunity. It should be tied to PGND at the return of the power stage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 7          | СОМР   | Input to the pulse width modulator. An external optocoupler connected between the REF and COMP pin sources current into an internal current mirror. The maximum duty ratio is achieved when no current is sourced by the optocoupler. The duty cycle reduces to zero once the source current exceeds 850 $\mu$ A. The internal current mirror improves the frequency response by reducing the ac voltage across the optocoupler transistor                                                                                                                                                                                                                                                                                                                                                                                                                                   |

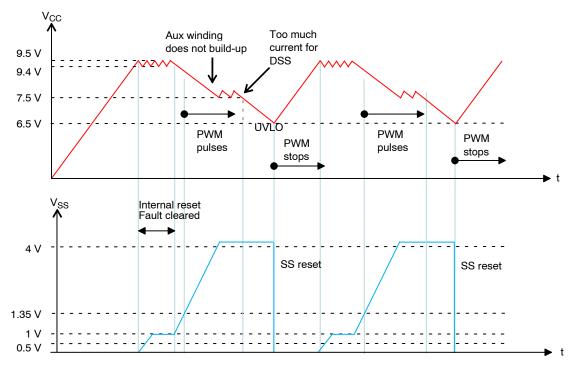

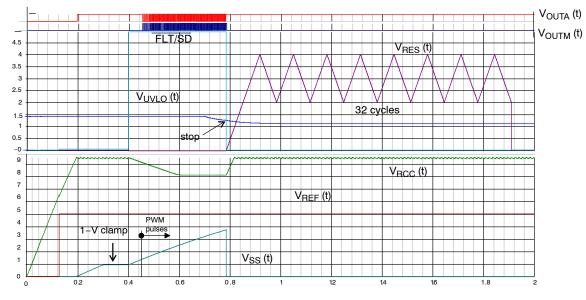

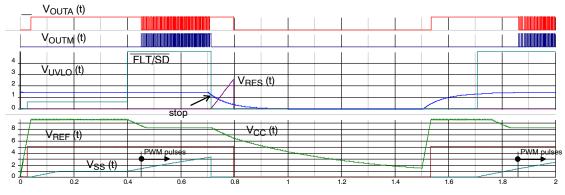

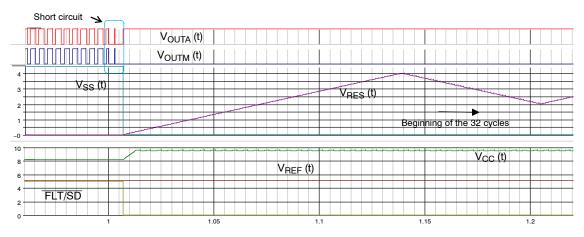

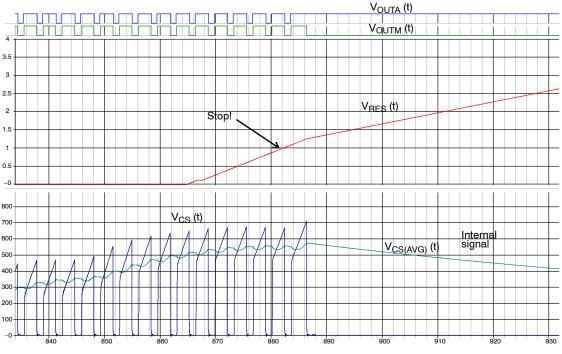

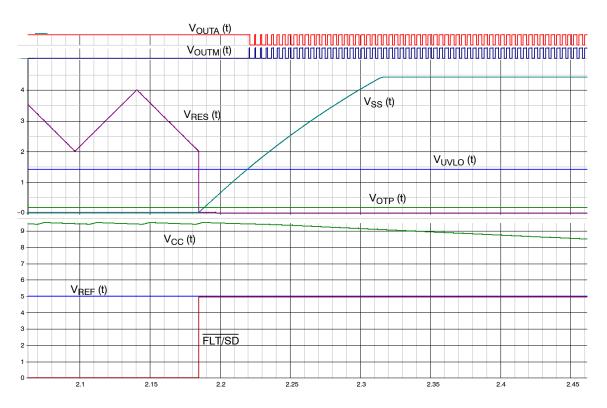

| 8          | RES    | Restart time control. A capacitor between this pin and AGND set the shutdown delay and hiccup mode restart delay time. If a restart fault is detected, a pull-up current source, $I_{RES(SRC1)}$ , typically 20 µA is enabled. If the RES pin voltage, $V_{RES}$ , exceeds the restart threshold, $V_{RES(TH)}$ , typically 1 V, the controller enters restart mode. $I_{RES(SRC1)}$ is disabled once in restart mode and a second pull up current source, $I_{RES(SRC2)}$ , typically 5 µA enabled. $I_{RES(SRC2)}$ is disabled once $V_{RES}$ reaches $V_{RES(peak)}$ , typically 4 V. A pull-down current source, $I_{RES(SNK)}$ , typically 5 µA, is enabled until VRES falls below $V_{RES(valley)}$ typically 2 V. The controller restarts after 32 $V_{RES}$ charge/discharge cycles                                                                                  |

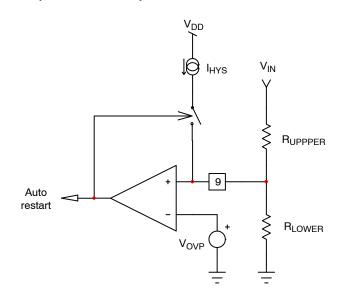

| 9          | OVP    | When this pin is biased beyond 1.25 V, all pulses immediately stop and the controller resumes operations after 32 $V_{\rm RES}$ charge/discharge cycles                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

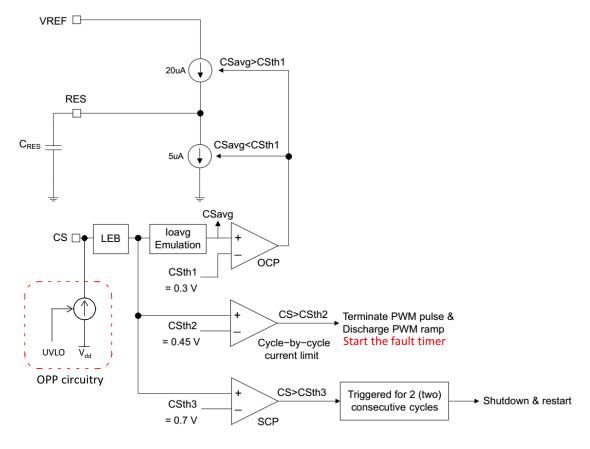

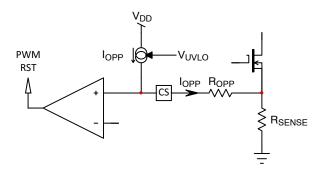

| 10         | CS     | Current sense input. The current sense signal is used for current-mode control, adaptive dead time control, cycle-by-cycle current limiting, over-current protection and short circuit protection, etc.<br>If the CS voltage exceeds the cycle by cycle current limit threshold, V <sub>ILIM</sub> , typically 0.45 V, the drive pulse is terminated. Internal leading edge blanking prevents triggering of the cycle by cycle current limit during normal operation. A short circuit condition exists if V <sub>CS</sub> exceeds the short-circuit threshold, V <sub>ILIM</sub> (SC), typically set to 0.7 V, during two consecutive clock pulses. By inserting a resistor in series with the sense current information, it is possible to create a voltage offset proportional to the input voltage and thus affects the maximum power the converter delivers at high line |

| 11         | REF    | Precision 5 V reference. Maximum output current is 12 mA. It is required to bypass the reference with a capacitor. The recommended capacitance ranges between 0.1 to 0.47 $\mu F$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 12         | OTP    | Over-temperature protection. A voltage divider containing a NTC connects to this pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

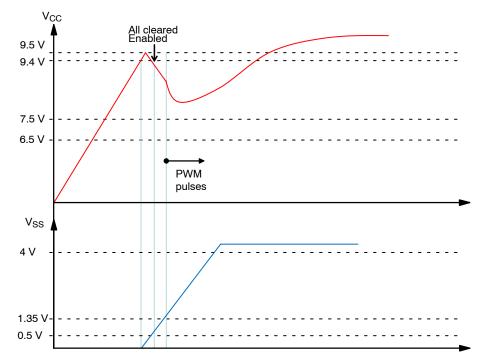

| 13         | VCC    | Positive input supply. This pin connects to an external capacitor for energy storage. An internal current source, $I_{start}$ , supplies current from $V_{in}$ to this pin. Once $V_{CC}$ reaches $V_{CC(on)}$ , typically 9.5 V, the startup current source is disabled. The current source is enabled once $V_{CC}$ falls below $V_{CC(off1)}$ , typically 9.4 V, while faults are present. Once faults are removed and the controller is operating, the startup current source turn–on threshold is reduced to $V_{CC(off2)}$ , typically 7.5 V                                                                                                                                                                                                                                                                                                                           |

| 14         | OUTM   | Main switch gate control. OUTM can source 2 A and sink 3 A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 15         | PGND   | Ground connection for OUTM and OUTA. Tie to the power stage return with a short loop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 16         | OUTA   | Active clamp switch gate control. OUTA has an adjustable leading and trailing edge overlap delay against OUTM. OUTA can source 2 A and sink 1 A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 17         | FLT/SD | Fault report and shutdown control. This is a dual-function bi-directional pin. This pin is an open-collector output with a 10 k $\Omega$ internal pull-up resistance connected to REF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Pin Number | Name            | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 18         | REFA            | Internally connected to REF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

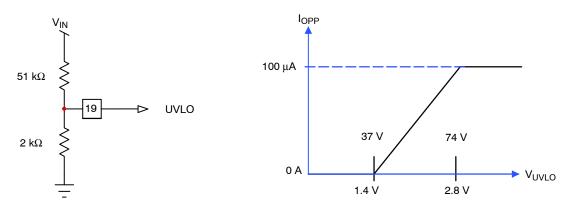

| 19         | UVLO            | Input voltage undervoltage detector. The input voltage is scaled down and sampled by means of a resistor divider. The controller enters standby mode once the UVLO voltage, V <sub>UVLO</sub> , exceeds the standby threshold, V <sub>STBY</sub> , typically 0.4 V. The controller enters shutdown mode if V <sub>UVLO</sub> falls below V <sub>STBY</sub> by the shutdown hysteresis level. The controller is enabled once V <sub>UVLO</sub> exceeds the enable threshold, V <sub>enable</sub> , typically 1.25 V. Hysteresis is provided by an internal pull-down current source, I <sub>UVLO</sub> , typically 20 $\mu$ A. The current source is disabled once the controller is enabled |

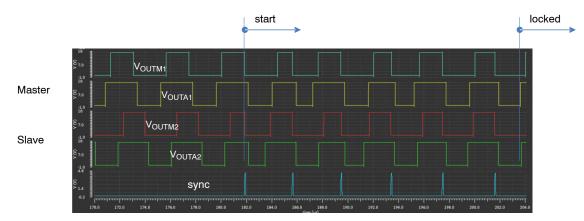

| 20         | SYNC            | This bi-directional pin is used to synchronize the controller or synchronize another controller driven by this pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 21         | NC              | No connect (creepage distance)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 22         | V <sub>IN</sub> | High voltage startup circuit input. Connect the input line voltage directly to this pin to enable the internal startup regulator. A constant current source supplies current from this pin to the capacitor connected to the VCC pin, eliminating the need for a startup resistor. The minimum charge current is 40 mA. The operating voltage range of the startup circuit is 13 V to 120 V                                                                                                                                                                                                                                                                                                 |

| 23         | NC              | No connect (creepage distance)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 24         | VSCLAMP         | Volt-second clamp. An external R-C divider from the input line generates a voltage ramp. This ramp is compared to a voltage reference, V <sub>SLIMIT</sub> , typically 1.5 V. The OUTM pulse is terminated once the ramp voltage exceeds V <sub>SLIMIT</sub> , thus limiting the maximum volt-second product of the main transformer. In voltage mode, VSCLAMP and RAMP pins can be tied together to share one external R-C circuit                                                                                                                                                                                                                                                         |

## Table 1. DETAILED PIN DESCRIPTION (continued)

## Table 2. MAXIMUM RATINGS

| Rating                                                                     | Symbol                                             | Value                   | Unit |

|----------------------------------------------------------------------------|----------------------------------------------------|-------------------------|------|

| High Voltage Startup Circuit Input Voltage – Continuous operation (Note 1) | V <sub>IN</sub>                                    | -0.3 to 120             | V    |

| High Voltage Startup Circuit Input Current                                 | I <sub>IN</sub>                                    | 70                      | mA   |

| UVLO Input Voltage                                                         | V <sub>UVLO</sub>                                  | -0.3 to V <sub>CC</sub> | V    |

| OTP Input Voltage                                                          | V <sub>OTP</sub>                                   | -0.3 to 7               | V    |

| Ramp Input Voltage                                                         | V <sub>Ramp</sub>                                  | -0.3 to 7               | V    |

| OVP Input Voltage                                                          | V <sub>OVP</sub>                                   | -0.3 to 7               | V    |

| Sync Input Voltage                                                         | V <sub>Sync</sub>                                  | -0.3 to 7               | V    |

| Ramp Peak Input Current                                                    | I <sub>Ramp</sub>                                  | 1                       | А    |

| VSClamp Input Voltage                                                      | V <sub>SCLAMP</sub>                                | -0.3 to 7               | V    |

| VSClamp Input Current                                                      | I <sub>SCLAMP</sub>                                | 0.5                     | mA   |

| RT Input Voltage                                                           | V <sub>RT</sub>                                    | -0.3 to 7               | V    |

| RT Input Current                                                           | I <sub>RT</sub>                                    | 2                       | mA   |

| COMP Input Voltage                                                         | V <sub>COMP</sub>                                  | -0.3 to 5.5             | V    |

| COMP Input Current                                                         | ICOMP                                              | 1                       | mA   |

| Reference Input Voltage                                                    | V <sub>REF</sub>                                   | -0.3 to 7               | V    |

| Reference Input Current                                                    | I <sub>REF</sub>                                   | 20                      | mA   |

| Supply Input Voltage                                                       | V <sub>CC(MAX)</sub>                               | -0.3 to 20              | V    |

| Supply Input Current                                                       | I <sub>CC(MAX)</sub>                               | 70                      | mA   |

| Main Driver Maximum Voltage                                                | V <sub>OUTM</sub>                                  | -0.3 to V <sub>CC</sub> | V    |

| Main Driver Maximum Current                                                | I <sub>OUTM</sub> (SRC)<br>I <sub>OUTM</sub> (SNK) | 2<br>3                  | А    |

| Active Clamp Driver Maximum Voltage                                        | V <sub>OUTA</sub>                                  | –0.3 to V <sub>CC</sub> | V    |

### Table 2. MAXIMUM RATINGS (continued)

| Rating                                                                                                                                                         | Symbol                                           | Value        | Unit |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|--------------|------|

| Active Clamp Driver Maximum Current                                                                                                                            | I <sub>OUTA(SRC)</sub><br>I <sub>OUTA(SNK)</sub> | 2<br>1       | А    |

| Current Sense Input Voltage                                                                                                                                    | V <sub>CS</sub>                                  | -0.3 to 7    | V    |

| Current Sense Peak Input Current                                                                                                                               | I <sub>CS</sub>                                  | 0.5          | А    |

| Soft-Start Input Voltage                                                                                                                                       | V <sub>SS</sub>                                  | -0.3 to 7    | V    |

| Restart Input Voltage                                                                                                                                          | V <sub>RES</sub>                                 | -0.3 to 7    | V    |

| Restart Peak Input Current                                                                                                                                     | I <sub>RES</sub>                                 | 0.1          | А    |

| FLT/SD Input Voltage                                                                                                                                           | V <sub>FLT/SD</sub>                              | -0.3 to 7    | V    |

| FLT/SD Peak Input Current                                                                                                                                      | I <sub>FLT/SD</sub>                              | 0.1          | А    |

| Deadtime Input Voltage                                                                                                                                         | V <sub>DT</sub>                                  | -0.3 to 7    | V    |

| Maximum Duty Ratio Control Input Voltage                                                                                                                       | V <sub>DLMT</sub>                                | -0.3 to 7    | V    |

| Maximum Duty Ratio Control Input Current                                                                                                                       | I <sub>DLMT</sub>                                | 2            | mA   |

| Maximum Operating Junction Temperature                                                                                                                         | TJ                                               | -40 to 150   | °C   |

| Storage Temperature Range                                                                                                                                      | T <sub>STG</sub>                                 | -60 to 150   | °C   |

| Lead Temperature (Soldering, 10 s)                                                                                                                             | T <sub>L(MAX)</sub>                              | 300          | °C   |

| Moisture Sensitivity Level                                                                                                                                     | MSL                                              | 1            | -    |

| Power Dissipation (TA = 25°C, 1 Oz Cu (35 μm), 0.155 Sq Inch (100 mm2)<br>Printed Circuit Copper Clad (Note 3)<br>MNTXG Suffix, Plastic Package (QFN–24)       | P <sub>D</sub>                                   | 760          | mW   |

| Thermal Resistance, Junction to Ambient 1 Oz Cu (35 $\mu$ m) 2–Layer 100 mm2<br>Printed Circuit Copper Clad (Note 3)<br>MNTXG Suffix, Plastic Package (QFN–24) | R <sub>θJA</sub>                                 | 131          | °C/W |

| Thermal Resistance, Junction to Case 2 Oz Cu (70 $\mu m$ ) 2–Layer 100 $mm^2$ Printed Circuit Copper Clad (Note 3) MNTXG Suffix, Plastic Package (QFN–24)      | R <sub>θJA</sub>                                 | 115          | °C/W |

| Junction to Top Psi (ψ) 1 Oz Cu (35 μm) 2–Layer 100 mm²<br>Printed Circuit Copper Clad (Note 3)<br>MNTXG Suffix, Plastic Package (QFN–24)                      | ΨθJT                                             | 22           | °C/W |

| Junction to Board Psi (ψ), 1 Oz Cu (35 μm) 2–Layer 100 mm²<br>Printed Circuit Copper Clad (Note 3)<br>MNTXG Suffix, Plastic Package (QFN–24)                   | ΨθЈВ                                             | 5.4          | °C/W |

| ESD Capability<br>Human Body Model per JEDEC Standard JESD22–A114F<br>Charge Device Model per JEDEC Standard JESD22–C101F                                      |                                                  | 2000<br>1500 | V    |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

This device contains Latch–Up protection and exceeds ±100 mA per JEDEC Standard JESD78.

As specified for a JEDEC EIA/JESD 51.3 conductivity test. Test conditions were under natural convection of zero air flow.

V<sub>IN</sub> is the exception.

#### Table 3. ELECTRICAL CHARACTERISTICS

$(C_{REF} = 0.1 \ \mu\text{F}, \ V_{in} = 48 \ \text{V}, \ V_{UVLO} = 2 \ \text{V}, \ V_{CC} = 10 \ \text{V}, \ V_{CS} = 0.25 \ \text{V}, \ R_{DLMT} = 49.9 \ \text{k}\Omega, \ R_{DT} = 100 \ \text{k}\Omega, \ R_{T} = 15.4 \ \text{k}\Omega, \ \text{for typical values } T_{J} = 25 \ ^{\circ}\text{C}, \ \text{for min/max values}, \ T_{J} \ \text{is} - 40 \ ^{\circ}\text{C} \ \text{to} \ 125 \ ^{\circ}\text{C}, \ \text{unless otherwise noted})$

| Characteristics                                                                         | Conditions                                                                                                                                                                           | Symbol                                                                  | Min               | Тур               | Max               | Unit |

|-----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|-------------------|-------------------|-------------------|------|

| STARTUP AND SUPPLY CIRCUIT                                                              | ſS                                                                                                                                                                                   |                                                                         |                   |                   |                   |      |

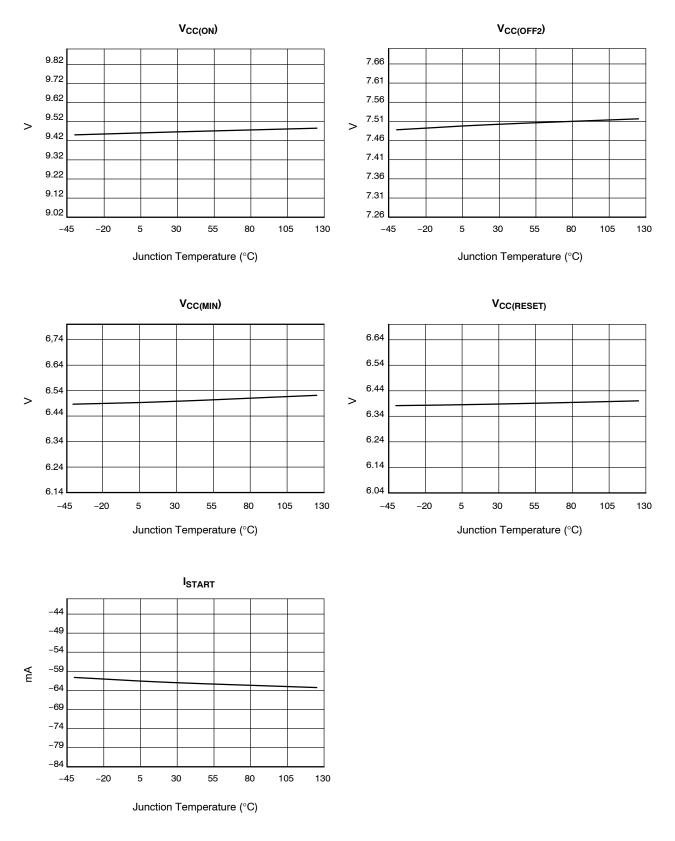

| Supply Voltage<br>Upper Regulation Level<br>Lower Regulation While<br>Disabled          | $V_{CC}$ increasing $V_{CC}$ decreasing                                                                                                                                              | V <sub>CC(on)</sub><br>V <sub>CC(off1)</sub>                            | 9.1<br>9.0        | 9.5<br>9.4        | 9.9<br>9.8        | V    |

| Lower Regulation While Enabled<br>Minimum Operating Voltage<br>Reset Voltage            | $V_{CC}$ decreasing $V_{CC}$ decreasing $V_{CC}$ decreasing                                                                                                                          | V <sub>CC(off2)</sub><br>V <sub>CC(MIN)</sub><br>V <sub>CC(reset)</sub> | 7.3<br>6.2<br>6.1 | 7.5<br>6.5<br>6.4 | 7.7<br>6.8<br>6.7 |      |

| Startup Delay                                                                           | Delay from $V_{CC(on)}$ to Enable                                                                                                                                                    | t <sub>delay(start)</sub>                                               | 30                | -                 | 125               | μs   |

| Delay in turning start-up source<br>off                                                 | V <sub>cc</sub> > V <sub>CC(off2)</sub>                                                                                                                                              | t <sub>Vcc(off2)</sub>                                                  |                   | 3                 | 10                | μs   |

| Delay in turning start-up<br>source on                                                  | V <sub>cc</sub> < V <sub>CC(off2)</sub>                                                                                                                                              | t <sub>Vcc(on2)</sub>                                                   |                   | 15                | 30                | μs   |

| Startup Current                                                                         | $V_{CC} = V_{CC(on)} - 0.2 V,$<br>$V_{in} = 48 V$                                                                                                                                    | I <sub>start</sub>                                                      | 40                | 55                | _                 | mA   |

| Startup Circuit Off-State<br>Leakage Current                                            | V <sub>in</sub> = 120 V                                                                                                                                                              | I <sub>Vin(off)</sub>                                                   | -                 | -                 | 100               | μA   |

| Minimum Startup Voltage                                                                 | $\begin{array}{l} I_{start} = 15 \text{ mA}, \\ V_{CC} = V_{CC(on)} - 0.2 \text{ V} \end{array}$                                                                                     | V <sub>in(MIN)</sub>                                                    | _                 | -                 | 15                | V    |

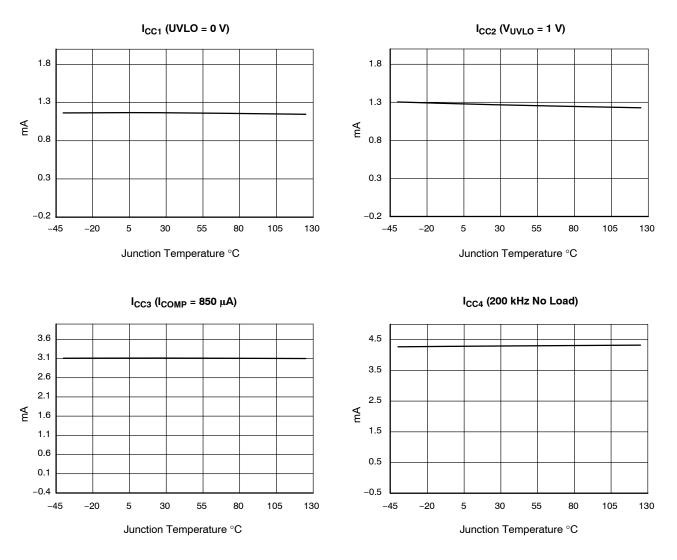

| Supply Current<br>Disabled mode current<br>Standby<br>No Switching<br>Operating Current | UVLO below 0.4 V<br>$V_{CC} = 10 \text{ V}, V_{UVLO} = 1 \text{ V}$<br>$V_{CC} = 10 \text{ V}, I_{COMP} = 850 \ \mu\text{A}$<br>f = 200  kHz,<br>$C_{OUTM} = C_{OUTA} = \text{open}$ | ICC1<br>ICC2<br>ICC3<br>ICC4                                            |                   | _<br>_<br>_<br>_  | 2<br>2<br>4<br>5  | mA   |

| REFERENCE                                                                               |                                                                                                                                                                                      |                                                                         |                   |                   |                   |      |

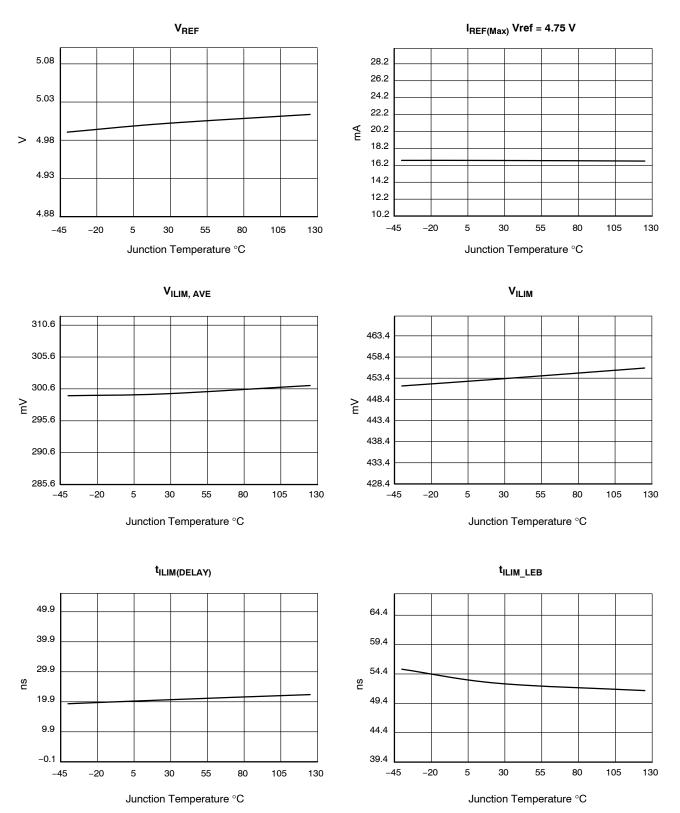

| Reference Voltage                                                                       | I <sub>REF</sub> = 0 mA                                                                                                                                                              | V <sub>REF</sub>                                                        | 4.9               | 5.0               | 5.1               | V    |

| Load Regulation                                                                         | I <sub>REF</sub> = 0 to 10 mA                                                                                                                                                        | V <sub>REF(load-reg)</sub>                                              | 4.85              | 5.00              | 5.15              | V    |

| Step Load Response                                                                      | I <sub>REF</sub> = 5 to 10 mA,<br>d <sub>I</sub> /d <sub>t</sub> = 100 mA / μs                                                                                                       | V <sub>REF(step-reg)</sub>                                              | 4.85              | 5.00              | 5.15              | V    |

| Source Current                                                                          | V <sub>REF</sub> = 4.75 V                                                                                                                                                            | I <sub>REF(MAX)</sub>                                                   | 12                | -                 | -                 | mA   |

| Minimum Decoupling<br>Capacitance                                                       |                                                                                                                                                                                      | C <sub>REF(range)</sub>                                                 | 0.1               | -                 | _                 | μF   |

| Reference Undervoltage<br>Threshold                                                     | V <sub>REF</sub> increasing                                                                                                                                                          | V <sub>REF(UVLO)</sub>                                                  |                   | 4.5               | 4.75              | V    |

| Reference Undervoltage<br>Hysteresis                                                    | V <sub>REF</sub> decreasing                                                                                                                                                          | V <sub>REF(HYS)</sub>                                                   |                   | 200               |                   | mV   |

| LINE VOLTAGE UVLO                                                                       |                                                                                                                                                                                      |                                                                         |                   |                   |                   |      |

| Standby Decreasing                                                                      | V <sub>UVLO</sub> decreasing                                                                                                                                                         | V <sub>STBY</sub>                                                       | 0.2               | 0.3               | 0.4               | V    |

| Enable Threshold                                                                        | V <sub>UVLO</sub> increasing                                                                                                                                                         | V <sub>enable</sub>                                                     | 1.23              | 1.25              | 1.27              | V    |

| Disable Filter Delay                                                                    | V <sub>UVLO</sub> = V <sub>enable</sub> – 400 mV                                                                                                                                     | t <sub>enable(delay2)</sub>                                             | 0.5               | -                 | 1                 | μs   |

| Pull-Down Current in Standby<br>Mode                                                    | V <sub>UVLO</sub> = V <sub>enable</sub> - 0.1 V<br>V <sub>SHDN</sub> < V <sub>UVLO</sub> < V <sub>enable</sub>                                                                       | I <sub>STBY</sub>                                                       | 18                | 20                | 22                | μA   |

| Pull–Down Resistor while I <sub>STBY</sub> is Disabled                                  | V <sub>UVLO</sub> = 1.25 V                                                                                                                                                           | R <sub>UVLO</sub>                                                       | 22.4              | 32.0              | 41.6              | kΩ   |

#### Table 3. ELECTRICAL CHARACTERISTICS (continued)

$(C_{REF} = 0.1 \ \mu\text{F}, V_{in} = 48 \ V, V_{UVLO} = 2 \ V, V_{CC} = 10 \ V, V_{CS} = 0.25 \ V, R_{DLMT} = 49.9 \ k\Omega, R_{DT} = 100 \ k\Omega, R_{T} = 15.4 \ k\Omega$ , for typical values T<sub>J</sub> = 25 °C, for min/max values, T<sub>J</sub> is - 40 °C to 125 °C, unless otherwise noted)

| Characteristics                                                                                       | Conditions                                                                          | Symbol                                             | Min    | Тур  | Max  | Unit |

|-------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|----------------------------------------------------|--------|------|------|------|

| MAIN GATE DRIVE                                                                                       |                                                                                     |                                                    |        |      |      |      |

| Rise Time (10–90%)                                                                                    | from 10 to 90% of V <sub>OUTM</sub> , $C_{OUTM} = 2.2 \text{ nF}$                   | t <sub>OUTM(rise)</sub>                            | _      | 8.8  | 17.6 | ns   |

| Fall Time (90-10%)                                                                                    | 90 to 10% of V <sub>OUTM</sub> ,<br>C <sub>OUTM</sub> = 2.2 nF                      | t <sub>OUTM(fall)</sub>                            | -      | 6.0  | 12   | ns   |

| Current Capability                                                                                    |                                                                                     |                                                    |        |      |      | Α    |

| Source<br>Sink                                                                                        | $V_{OUTM} = 4 V$<br>$V_{OUTM} = 4 V$ , $V_{CC} = 7.5 V$ ,<br>$I_{COMP} = 850 \mu A$ | I <sub>OUTM</sub> (SRC)<br>I <sub>OUTM</sub> (SNK) | 2<br>3 |      |      |      |

| High State Voltage Offset                                                                             | $V_{CC} - V_{OUTM}, V_{CC} = 8 V,$<br>$C_{OUTM} = 2.2 \text{ nF}$                   | V <sub>OUTM(offset)</sub>                          | _      | -    | 0.2  | V    |

| ow Stage Voltage V <sub>UVLO</sub> = 1 V                                                              |                                                                                     | V <sub>OUTM(low)</sub>                             | -      | -    | 0.2  | V    |

| ACTIVE CLAMP GATE DRIVE                                                                               | I                                                                                   |                                                    |        |      |      |      |

| Rise Time (10–90%)         from 10 to 90% of V <sub>OUTA</sub> ,           C <sub>OUTA</sub> = 2.2 nF |                                                                                     | t <sub>OUTA(rise)</sub>                            | -      | 8.8  | 17.6 | ns   |

| Fall Time (90-10%)                                                                                    | 90 to 10% of V <sub>OUTA</sub> ,<br>C <sub>OUTA</sub> = 2.2 nF                      | t <sub>OUTA(fall)</sub>                            | _      | 17.6 | 35.2 | ns   |

| Current Capability<br>Source<br>Sink                                                                  | V <sub>OUTA</sub> = 4 V<br>V <sub>OUTA</sub> = 4 V, V <sub>CC</sub> = 7.5 V         | Iouta(src)<br>Iouta(snk)                           | 2<br>1 |      |      | A    |

| High State Voltage Offset                                                                             | $V_{CC} - V_{OUTA}, V_{CC} = 8 V,$<br>$C_{OUTA} = 2.2 \text{ nF}$                   | V <sub>OUTA(offset)</sub>                          | -      | -    | 0.2  | V    |

| Low Stage Voltage                                                                                     | V <sub>UVLO</sub> = 1 V                                                             | V <sub>OUTA(low)</sub>                             | _      | -    | 0.2  | V    |

| CURRENT SENSE                                                                                         |                                                                                     |                                                    |        |      |      | •    |

| Average Current Limit Threshold                                                                       |                                                                                     | V <sub>ILIM(ave)</sub>                             | 288    | 300  | 312  | mV   |

| Average Current Limit Leading<br>Edge Blanking Duration                                               |                                                                                     | t <sub>ILIMAVE</sub> (LEB)                         | 23     | 30   | 37   | ns   |

| Average Current Limit<br>Propagation Delay                                                            |                                                                                     | t <sub>ILIMAVE(delay)</sub>                        | -      | 40   | -    | ns   |

| Cycle by Cycle Current Limit<br>Threshold                                                             |                                                                                     | V <sub>ILIM</sub>                                  | 432    | 450  | 468  | mV   |

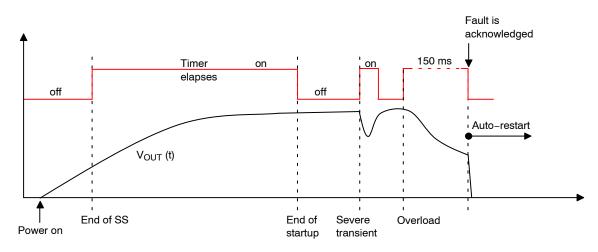

| Over Current Timer when V <sub>ILIM</sub> is reached                                                  |                                                                                     | t <sub>OVLD</sub>                                  | 150    | 180  |      | ms   |

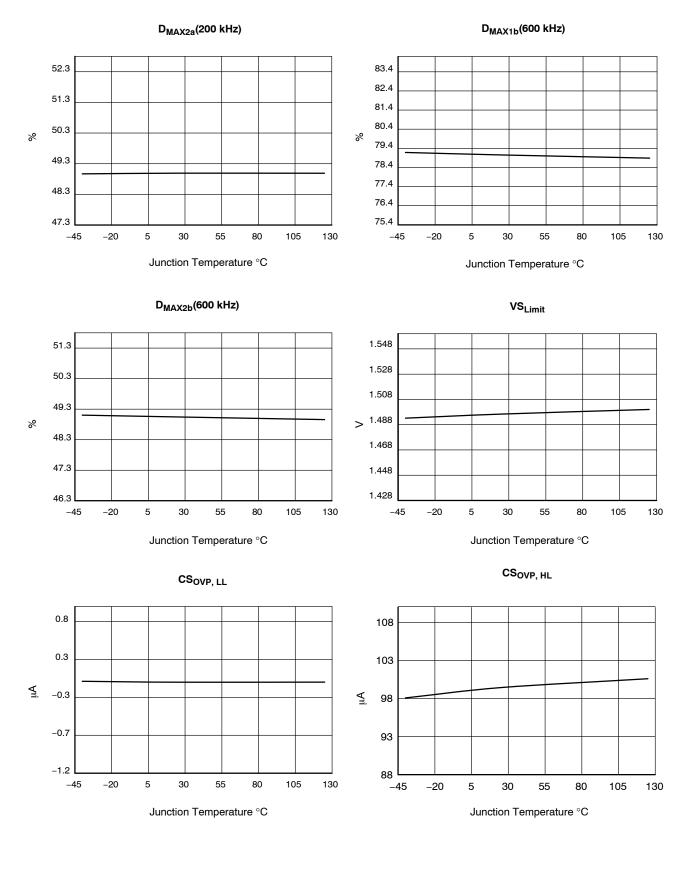

| Current Sourced by CS low line                                                                        | Over Power Protection<br>current – V <sub>UVLO</sub> = 1.4 V                        | CS <sub>OVPL</sub>                                 |        | 0    |      | μA   |

| Current Sourced by CS high line                                                                       | Over Power Protection<br>current – V <sub>UVLO</sub> = 2.8 V                        | CS <sub>OVPH</sub>                                 | 90     | 100  | 110  | μA   |

| Cycle by Cycle Current Limit<br>Leading Edge Blanking Duration                                        |                                                                                     | t <sub>ILIM(LEB)</sub>                             | 42     | 55   | 68   | ns   |

| Cycle by Cycle Current Limit<br>Propagation Delay                                                     | Step V <sub>CS</sub> to 0.7 V to OUTM falling edge, dV/dt = 20 V/ $\mu$ s           | t <sub>ILIM(delay)</sub>                           | _      | 40   | 56   | ns   |

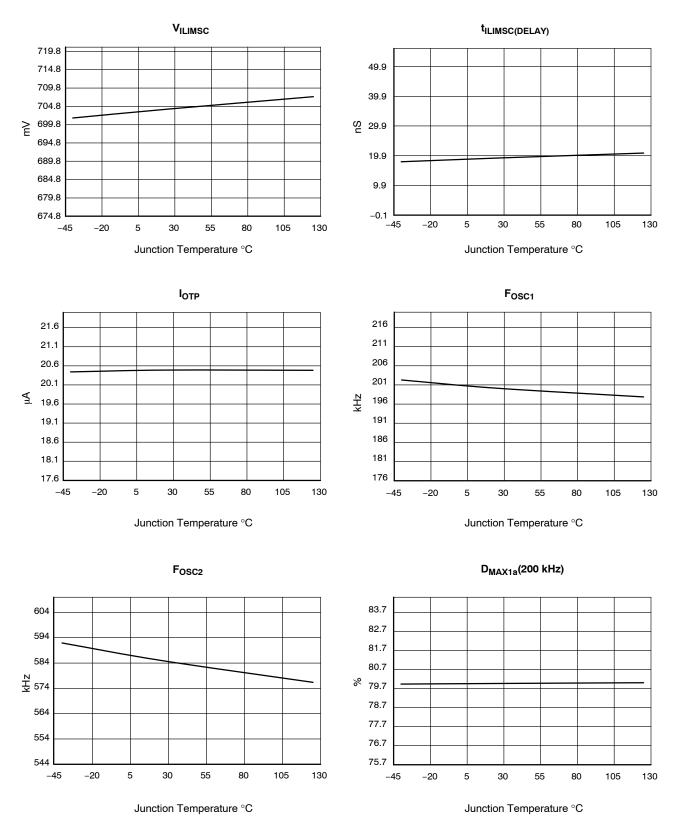

| Short Circuit Current Limit<br>Threshold                                                              |                                                                                     | V <sub>ILIM(SC)</sub>                              | 679    | 700  | 721  | mV   |

| Short Circuit Current Limit<br>Leading Edge Blanking Duration                                         |                                                                                     | t <sub>ILIMSC</sub> (LEB)                          | 23     | 30   | 37   | ns   |

| Short–Circuit Current Limit<br>Propagation Delay                                                      | Step V <sub>CS</sub> to 0.9 V to OUTM falling edge, dV/dt = 10 V/ $\mu$ s           | <sup>t</sup> ILIMSC(delay)                         | _      | 40   | 56   | ns   |

| Short Circuit Counter                                                                                 | Step V <sub>CS</sub> to V <sub>ILIM(SC)</sub> + 0.2 V                               | n <sub>ILIMSC</sub>                                | _      | 2    | _    | -    |

### Table 3. ELECTRICAL CHARACTERISTICS (continued)

$(C_{REF} = 0.1 \ \mu\text{F}, V_{in} = 48 \ V, V_{UVLO} = 2 \ V, V_{CC} = 10 \ V, V_{CS} = 0.25 \ V, R_{DLMT} = 49.9 \ k\Omega, R_{DT} = 100 \ k\Omega, R_{T} = 15.4 \ k\Omega$ , for typical values T<sub>J</sub> = 25 °C, for min/max values, T<sub>J</sub> is - 40 °C to 125 °C, unless otherwise noted)

| Characteristics                        | Conditions                                                                                                                                                                             | Symbol                                           | Min     | Тур     | Max     | Unit |

|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|---------|---------|---------|------|

| CURRENT SENSE                          |                                                                                                                                                                                        |                                                  |         |         |         |      |

| Discharge Switch On Resistance         | $V_{SCLAMP} = 2 V,$<br>$V_{CS} = 100 mV$                                                                                                                                               | R <sub>CSswitch(on)</sub>                        | _       | -       | 35      | Ω    |

| OVERTEMPERATURE PROTECT                | ION (OTP)                                                                                                                                                                              |                                                  |         | •       |         |      |

| Overtemperature Detection<br>Threshold | V <sub>OTP</sub> increasing                                                                                                                                                            | V <sub>OTP(TH)</sub>                             | 1.23    | 1.25    | 1.27    | V    |

| Overtemperature Detection<br>Delay     | $V_{OTP} = V_{OTP(TH)} - 20 \text{ mV}$                                                                                                                                                | t <sub>OTP(delay)</sub>                          | 10      | 20      | 30      | μs   |

| Pull-up Current in OTP Mode            | $V_{OTP} = V_{OTP(TH)} + 0.1 V$                                                                                                                                                        | I <sub>OTP</sub>                                 | 18      | 20      | 22      | μA   |

| OVERVOLTAGE PROTECTION (C              | OVP)                                                                                                                                                                                   |                                                  |         |         |         |      |

| Overvoltage Detection Threshold        | V <sub>OVP</sub> increasing                                                                                                                                                            | V <sub>OVP(TH)</sub>                             | 1.23    | 1.25    | 1.27    | V    |

| Time Constant to Confirmation          |                                                                                                                                                                                        | t <sub>OVP(TH)</sub>                             |         | 0       |         | μs   |

| Hysteresis current                     | Active when OVP is<br>acknowledged                                                                                                                                                     | I <sub>HYS</sub>                                 | 18      | 20      | 22      | μA   |

| SOFT-START                             |                                                                                                                                                                                        | -                                                |         |         |         |      |

| Soft-Start Charge Current              | $V_{SS}$ = 1.5 V to 3 V                                                                                                                                                                | I <sub>SS</sub>                                  | 18      | 20      | 22      | μA   |

| Soft-Start Onset Threshold             |                                                                                                                                                                                        | V <sub>SS(offset)</sub>                          |         | 1.35    |         | V    |

| Clamp Voltage                          |                                                                                                                                                                                        | V <sub>SS(clamp)</sub>                           |         | 0.85    |         | V    |

| Discharge Switch On Resistance         | V <sub>SS</sub> = 100 mV                                                                                                                                                               | R <sub>SSswitch(on)</sub>                        | -       | -       | 30      | Ω    |

| Disable Threshold                      | V <sub>SS</sub> decreasing                                                                                                                                                             | V <sub>SS(disable)</sub>                         | 0.4     | 0.5     | 0.6     | V    |

| RESTART                                |                                                                                                                                                                                        |                                                  |         |         |         |      |

| Restart Delay Threshold                | V <sub>RES</sub> increasing                                                                                                                                                            | V <sub>RES(TH)</sub>                             | 0.96    | 1.00    | 1.04    | V    |

| Peak Voltage                           | V <sub>CS</sub> > V <sub>ILIMAVE</sub><br>V <sub>RES</sub> increasing                                                                                                                  | V <sub>RES(peak)</sub>                           | 3.8     | 4.0     | 4.2     | V    |

| Valley Voltage                         | V <sub>CS</sub> > V <sub>ILIMAVE</sub><br>V <sub>RES</sub> decreasing                                                                                                                  | V <sub>RES(valley)</sub>                         | 1.9     | 2.0     | 2.1     | V    |

| Discharge Current                      | V <sub>CS</sub> < V <sub>ILIMAVE</sub><br>V <sub>RES</sub> = 100 mV                                                                                                                    | I <sub>RES(SNK)</sub>                            | 4       | 5       | 6       | μA   |

| Charge Current                         | $\label{eq:VCS} \begin{array}{l} V_{CS} > V_{ILIMAVE}, \\ V_{RES} = V_{RES(valley)} - 50 \text{ mV} \\ V_{CS} > V_{ILIMAVE}, \\ V_{RES} = V_{RES(valley)} + 50 \text{ mV} \end{array}$ | I <sub>RES(SRC1)</sub><br>I <sub>RES(SRC2)</sub> | 18<br>4 | 20<br>5 | 22<br>6 | μA   |

| Restart Counter                        | V <sub>OTP</sub> > V <sub>OTP(TH)</sub>                                                                                                                                                | n <sub>RES</sub>                                 |         | 32      |         |      |

| Discharge Voltage                      |                                                                                                                                                                                        | V <sub>RES(DIS)</sub>                            | 50      | 100     | 150     | mV   |

| Discharge Switch On Resistance         | V <sub>RES</sub> = 200 mV                                                                                                                                                              | R <sub>ESswitch(on)</sub>                        | —       | -       | 110     | Ω    |

| FAULT REPORT AND REMOTE S              | HUTDOWN                                                                                                                                                                                |                                                  |         |         |         |      |

| Enable Threshold                       | V <sub>FLT/SD</sub> = increasing                                                                                                                                                       | V <sub>FLT(enable)</sub>                         | 1.37    | 1.45    | 1.53    | V    |

| Fault Threshold                        | V <sub>FLT/SD</sub> = decreasing                                                                                                                                                       | V <sub>fault</sub> FLT/SD                        | 1.23    | 1.25    | 1.27    | V    |

| Internal Pull-Up Resistor              | V <sub>FLT/SD</sub> = 3 V                                                                                                                                                              | R <sub>FAULT/SD</sub>                            | 8.5     | 10.0    | 11.5    | kΩ   |

| Discharge Switch On Resistance         | V <sub>FLT/SD</sub> = 3 V                                                                                                                                                              | R <sub>FAULTswitch(on)</sub>                     | -       | -       | 120     | Ω    |

#### Table 3. ELECTRICAL CHARACTERISTICS (continued)

$(C_{REF} = 0.1 \ \mu\text{F}, V_{in} = 48 \ \text{V}, V_{UVLO} = 2 \ \text{V}, V_{CC} = 10 \ \text{V}, V_{CS} = 0.25 \ \text{V}, R_{DLMT} = 49.9 \ \text{k}\Omega, R_{DT} = 100 \ \text{k}\Omega, R_{T} = 15.4 \ \text{k}\Omega, \text{ for typical values } T_{J} = 25 \ ^{\circ}\text{C}, \text{ for min/max values}, T_{J} \ \text{is} - 40 \ ^{\circ}\text{C} \ \text{to} \ 125 \ ^{\circ}\text{C}, \text{ unless otherwise noted})$

| Characteristics                                                      | Conditions                                                                                                                                                                                                                                                                                                                                                                                                                | Symbol                                       | Min                                   | Тур                                    | Max                                    | Unit |

|----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|---------------------------------------|----------------------------------------|----------------------------------------|------|

| OSCILLATOR                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                           |                                              |                                       |                                        |                                        |      |

| Operating Frequency Range                                            |                                                                                                                                                                                                                                                                                                                                                                                                                           | f <sub>range</sub>                           | 100                                   | -                                      | 1000                                   | kHz  |

| Oscillator Frequency $t_D \approx 100 \text{ ns}$                    | R <sub>T</sub> = 42.2 kΩ, R <sub>DT</sub> = 69.8 kΩ,                                                                                                                                                                                                                                                                                                                                                                      | f <sub>OSC1</sub>                            | 186                                   | 200                                    | 214                                    | kHz  |

| t <sub>D</sub> ≈ 75 ns                                               | R <sub>DLMT</sub> = 47.5 kΩ<br>R <sub>T</sub> = 13 kΩ, R <sub>DT</sub> = 52.3 kΩ,<br>R <sub>DLMT</sub> = 17 kΩ                                                                                                                                                                                                                                                                                                            | fosc2                                        | 558                                   | 600                                    | 642                                    |      |

| SYNCHRONIZATION                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                           |                                              |                                       |                                        |                                        |      |

| Sync Pin Input Voltage to "1"<br>level                               | Acknowledged high level                                                                                                                                                                                                                                                                                                                                                                                                   | V <sub>syncH</sub>                           | 2.8                                   | 3                                      | 3.4                                    | V    |

| Sync Pin Input Voltage to "0" Acknowledged low level level           |                                                                                                                                                                                                                                                                                                                                                                                                                           | V <sub>syncL</sub>                           | 1.4                                   | 1.6                                    | 1.8                                    | V    |

| Sync Input Pulse Width Minimum input width for proper sync operation |                                                                                                                                                                                                                                                                                                                                                                                                                           | t <sub>synicw</sub>                          | 50                                    |                                        |                                        | ns   |

| Sync Pullup Current                                                  | _                                                                                                                                                                                                                                                                                                                                                                                                                         | I <sub>syncPU</sub>                          | 0.45                                  | 0.6                                    | 0.75                                   | mA   |

| Sync Pulldown Current                                                | _                                                                                                                                                                                                                                                                                                                                                                                                                         | I <sub>syncPD</sub>                          | 1.4                                   | 1.6                                    | 1.8                                    | mA   |

| Sync Permanent Pulldown<br>Current                                   |                                                                                                                                                                                                                                                                                                                                                                                                                           | I <sub>syncPPD</sub>                         | 26                                    | 32                                     | 38                                     | μΑ   |

| Sync Output Width Output Pulse Width                                 |                                                                                                                                                                                                                                                                                                                                                                                                                           | t <sub>syncow</sub>                          | 130                                   | 180                                    | 230                                    | ns   |

| Sync to Output Delay                                                 | Rising edge of sync pulse to<br>OUTM rising edge                                                                                                                                                                                                                                                                                                                                                                          | t <sub>syncdel</sub>                         |                                       | 32                                     | 50                                     | ns   |

| MAXIMUM DUTY RATIO                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                           |                                              |                                       |                                        |                                        |      |

| Maximum Duty Ratio<br>f = 200 kHz                                    | $\label{eq:theta} \begin{array}{l} \mbox{Internal spec is } +\!\!/-3\%, \\ V_{UVLO} = 1.4 \ V \\ R_T = 15.4 \ k\Omega, \ R_{DT} = 69.8 \ k\Omega, \\ R_{DLMT} = 75 \ k\Omega \\ R_T = 42.2 \ k\Omega, \ R_{DT} = 69.8 \ k\Omega, \\ R_{DLMT} = 47.5 \ k\Omega \end{array}$                                                                                                                                                | D <sub>(MAX1a)</sub><br>D <sub>(MAX2a)</sub> | 76.5<br>47.8                          | 80.5<br>50.3                           | 84.5<br>52.8                           | %    |

| f = 600 kHz                                                          | $ \begin{array}{l} {R_{T}} = 4.02 \; k\Omega, \; {R_{DT}} = 52.3 \; k\Omega, \\ {R_{DLMT}} = 26.1 \; k\Omega \\ {R_{T}} = 13 \; k\Omega, \; {R_{DT}} = 52.3 \; k\Omega, \\ {R_{DLMT}} = 16.9 \; k\Omega \end{array} $                                                                                                                                                                                                     | D <sub>(MAX1b)</sub><br>D <sub>(MAX2b)</sub> | 76.2<br>46.8                          | 80.2<br>49.3                           | 84.2<br>51.8                           |      |

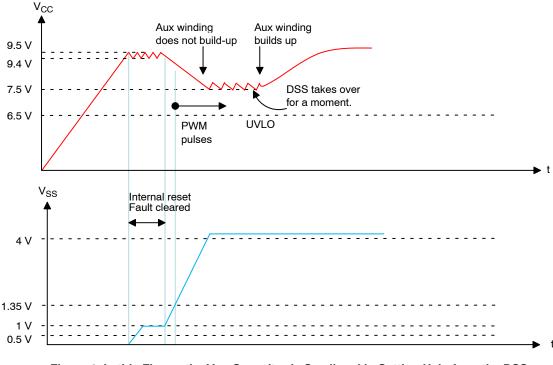

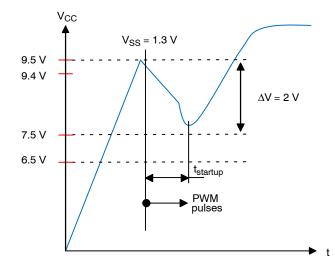

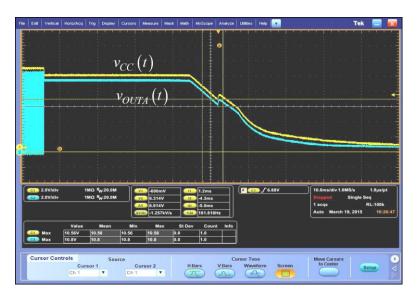

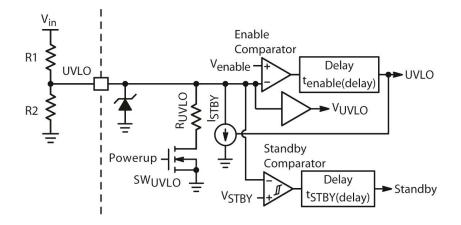

| Minimum Duty Ratio                                                   | I <sub>COMP</sub> = 850 μA                                                                                                                                                                                                                                                                                                                                                                                                | D <sub>(MIN)</sub>                           | _                                     | -                                      | 0                                      | %    |