### **ATPL Series Power Line Communications Device**

#### **DATASHEET**

### **Description**

ATPL230A is a power line communications base band modem, compliant with the PHY layer of PRIME (Power Line Intelligent Metering Evolution) specification. PRIME is an open standard technology used for Smart Grid applications like Smart Metering, Industrial Lighting and Automation, Home Automation, Street Lighting, Solar Energy and PHEV Charging Stations.

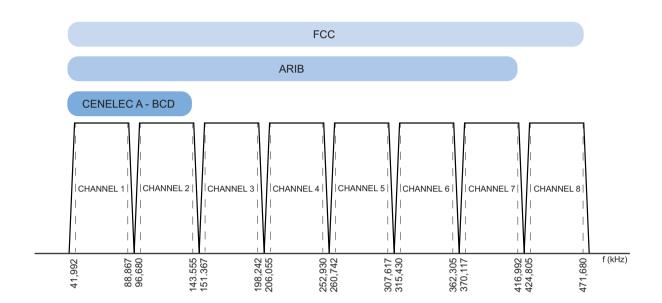

ATPL230A PRIME device includes enhanced features such as additional robust modes and frequency band extension. ATPL230A is able to operate in independently selectable transmission bands up to 472 kHz, achieving baud rates ranging from 5.4 kbps up to 128.6 kbps.

ATPL230A has been conceived to be bundled with an external Atmel<sup>®</sup> MCU or MPU. Atmel provides a PRIME PHY layer library which is used by the external MCU/MPU to take control of ATPL230A PHY layer device.

### 1. Features

- Modem

- Power Line Carrier Modem for 50 Hz and 60 Hz mains

- 97-carriers OFDM PRIME compliant

- DBPSK, DQPSK, D8PSK modulation schemes available

- Additional enhanced modes available: DBPSK Robust and DQPSK Robust

- Eight selectable channels between 42kHz and 472kHz available. Only one channel can be active at a time

- Baud rate Selectable: 5.4 to 128.6 kbps

- Four dedicated buffers for transmission/reception

- Up to 124.6 dBµVrms injected signal against PRIME load

- Up to 79.6 dB of dynamic range in PRIME networks

- Automatic Gain Control and continuous amplitude tracking in signal reception

- Class D switching power amplifier control

- Integrated 1.2V LDO regulator to supply analog functions

- Medium Access Control co-processor features

- Viterbi soft decoding and PRIME CRC calculation

- 128-bit AES encryption

- Channel sensing and collision pre-detection

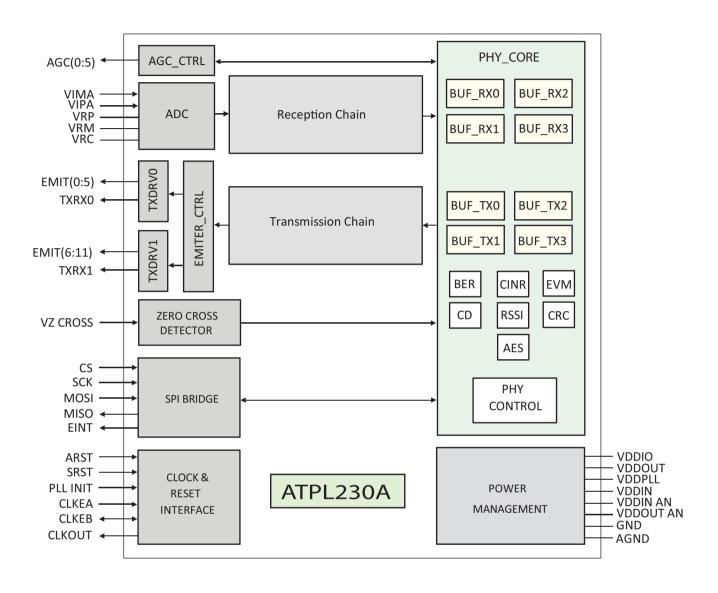

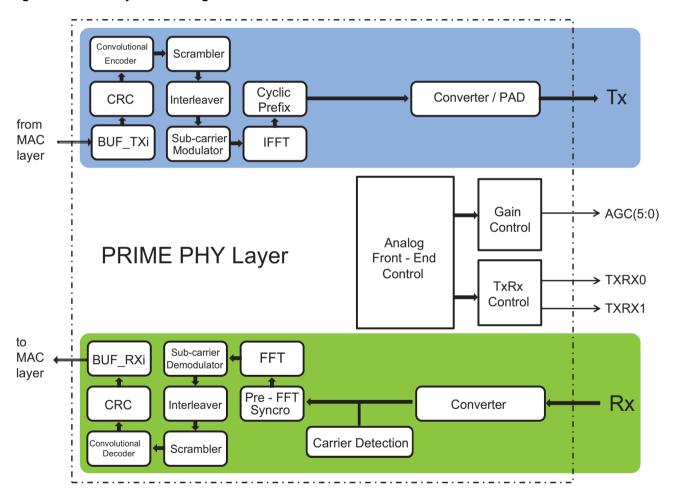

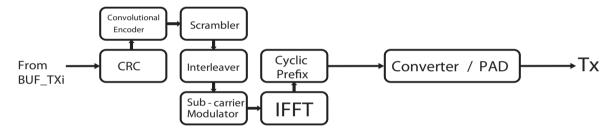

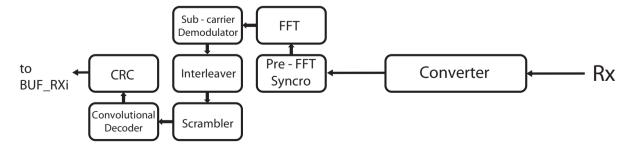

# 2. Block Diagram

Figure 2-1. ATPL230A Functional Block Diagram

# 3. Signal Description

Table 3-1. Signal Description List

| Signal Name                | Function                                                                                                                                                                                       | Туре       | Active<br>Level | Voltage reference | Comments                        |

|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-----------------|-------------------|---------------------------------|

|                            | Power S                                                                                                                                                                                        | upplies    |                 |                   |                                 |

| VDDIO                      | 3.3V digital supply. Digital power supply must be decoupled by external capacitors                                                                                                             | Power      |                 |                   | 3.0V to 3.6V                    |

| VDDIN                      | 3.3V Digital LDO input supply                                                                                                                                                                  | Power      |                 |                   | 3.0V to 3.6V                    |

| VDDIN AN                   | 3.3V Analog LDO input supply                                                                                                                                                                   | Power      |                 |                   | 3.0V to 3.6V                    |

| VDDOUT AN                  | 1.2V Analog LDO output. A capacitor in the range 0.1μF - 10μF must be connected to each pin                                                                                                    | Power      |                 |                   | 1.2V                            |

| VDDOUT                     | 1.2V Digital LDO output. A capacitor in the range 0.1μF - 10μF must be connected to each pin                                                                                                   | Power      |                 |                   | 1.2V                            |

| VDDPLL                     | 1.2V PLL supply. It must be decoupled by a 100nF external capacitor, and connected to VDDOUT through a filter (Cut off frequency: 25kHz)                                                       | Power      |                 |                   | 1.2V                            |

| GND <sup>(1)</sup>         | Digital Ground                                                                                                                                                                                 | Power      |                 |                   |                                 |

| AGND <sup>(1)</sup>        | Analog Ground                                                                                                                                                                                  | Power      |                 |                   |                                 |

|                            | Clocks, Oscillat                                                                                                                                                                               | tors and P | LLs             |                   |                                 |

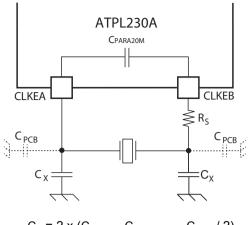

| CLKEA <sup>(2)</sup>       | External Clock Oscillator     CLKEA must be connected to one terminal of a crystal (when a crystal is being used) or used as input for external clock signal                                   | Input      |                 | VDDIO             |                                 |

| CLKEB <sup>(2)</sup>       | External Clock Oscillator     CLKEB must be connected to one terminal of a crystal (when a crystal is being used) or must be floating when an external clock signal is connected through CLKEA | I/O        |                 | VDDIO             |                                 |

| CLKOUT                     | 10MHz External Clock Output                                                                                                                                                                    | Output     |                 | VDDIO             |                                 |

|                            | Reset                                                                                                                                                                                          | Test       |                 |                   |                                 |

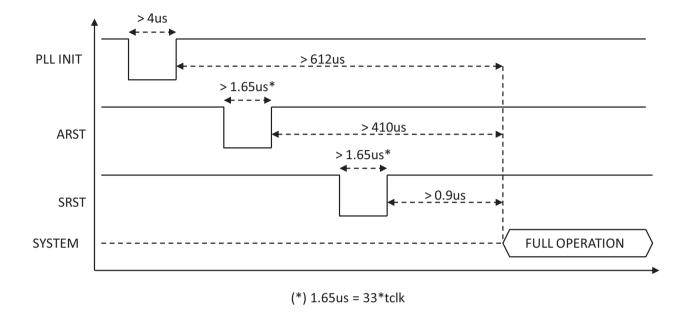

| ARST                       | Asynchronous Reset                                                                                                                                                                             | Input      | Low             | VDDIO             | Internal pull up <sup>(3)</sup> |

| SRST                       | Synchronous Reset                                                                                                                                                                              | Input      | Low             | VDDIO             | Internal pull up <sup>(3)</sup> |

| PLL INIT                   | PLL Initialization Signal                                                                                                                                                                      | Input      | Low             | VDDIO             | Internal pull up <sup>(3)</sup> |

|                            | PPLC (PRIME Power Line Co                                                                                                                                                                      | ommunica   | tions) Trar     | sceiver           |                                 |

| EMIT [0:11] <sup>(4)</sup> | PLC Tri-state Transmission ports                                                                                                                                                               | Output     |                 | VDDIO             |                                 |

| AGC [0:5]                  | Automatic Gain Control:     These digital tri-state outputs are managed by AGC hardware logic to drive external circuitry when input signal attenuation is needed                              | Output     |                 | VDDIO             |                                 |

Table 3-1. Signal Description List

| Signal Name             | Function                                                                                                                                                                                                                                                                  | Туре        | Active<br>Level | Voltage<br>reference | Comments                          |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-----------------|----------------------|-----------------------------------|

| TXRX0                   | Analog Front-End Transmission/Reception for TXDRV0  This digital output is used to modify external coupling behavior in Transmission/Reception. The suitable value depends on the external circuitry configuration. The polarity of this pin can be inverted by software. | Output      |                 | VDDIO                |                                   |

| TXRX1                   | Analog Front-End Transmission/Reception for TXDRV1  This digital output is used to modify external coupling behavior in Transmission/Reception. The suitable value depends on the external circuitry configuration. The polarity of this pin can be inverted by software. | Output      |                 | VDDIO                |                                   |

| VZ CROSS <sup>(5)</sup> | Mains Zero-Cross Detection Signal:     This input detects the zero-crossing of the mains voltage                                                                                                                                                                          | Input       |                 | VDDIO                | Internal pull down <sup>(3)</sup> |

| VIMA                    | Negative Differential Voltage Input                                                                                                                                                                                                                                       | Input       |                 | VDDOUT AN            |                                   |

| VIPA                    | Positive Differential Voltage Input                                                                                                                                                                                                                                       | Input       |                 | VDDOUT AN            |                                   |

| VRP                     | Internal Reference "Plus" Voltage. Connect an external decoupling capacitor between VRP and VRM (1nF - 100nF)                                                                                                                                                             | Output      |                 | VDDOUT AN            |                                   |

| VRM                     | Internal Reference "Minus" Voltage. Connect an external decoupling capacitor between VRP and VRM (1nF - 100nF)                                                                                                                                                            | Output      |                 | VDDOUT AN            |                                   |

| VRC                     | Common-mode Voltage. Bypass to analog ground with an external decoupling capacitor (100pF - 1nF)                                                                                                                                                                          | Output      |                 | VDDOUT AN            |                                   |

|                         | Serial Peripheral                                                                                                                                                                                                                                                         | Interface - | - SPI           |                      |                                   |

| CS                      | SPI CS SPI bridge Slave Select                                                                                                                                                                                                                                            | Input       | Low             | VDDIO                | Internal pull up <sup>(3)</sup>   |

| SCK                     | SPI SCK • SPI bridge Clock signal                                                                                                                                                                                                                                         | Input       |                 | VDDIO                | Internal pull up <sup>(3)</sup>   |

| MOSI                    | SPI MOSI  SPI bridge Master Out Slave In                                                                                                                                                                                                                                  | Input       |                 | VDDIO                | Internal pull up <sup>(3)</sup>   |

| MISO                    | SPI MISO • SPI bridge Master In Slave Out                                                                                                                                                                                                                                 | Output      |                 | VDDIO                |                                   |

| EINT                    | PHY Layer External Interrupt                                                                                                                                                                                                                                              | Output      | Low             | VDDIO                |                                   |

Notes: 1. Separate pins are provided for GND and AGND grounds. Layout considerations should be taken into account to reduce interference. Ground pins should be connected as shortly as possible to the system ground plane. For more details about EMC Considerations, please refer to AVR040 application note.

- 2. The crystal should be located as close as possible to CLKEA and CLKEB pins. See Table 10-7 on page 112.

- 3. See Table 10-5 on page 109.

- 4. Different configurations allowed depending on external topology and net behavior.

- 5. Depending on whether an isolated or a non-isolated power supply is being used, isolation of this pin should be taken into account in the circuitry design. Please refer to the Reference Design for further information.

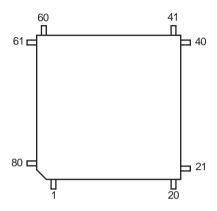

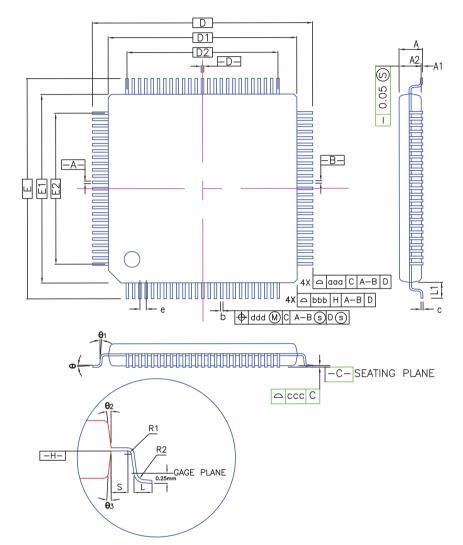

# 4. Package and Pinout

# 4.1 80-Lead LQFP Package Outline

Figure 4-1. Orientation of the 80-Lead LQFP Package

## 4.2 80-Lead LQFP Pinout

Table 4-1. 80 - Lead LQFP Pinout

| 1  | NC       | 21 | VDDIO  | 41 | GND    | 61 | GND       |

|----|----------|----|--------|----|--------|----|-----------|

| 2  | NC       | 22 | NC     | 42 | EMIT8  | 62 | AGND      |

| 3  | NC       | 23 | CLKOUT | 43 | EMIT9  | 63 | VDDOUT AN |

| 4  | ARST     | 24 | CS     | 44 | EMIT10 | 64 | VIMA      |

| 5  | PLL INIT | 25 | SCK    | 45 | EMIT11 | 65 | VIPA      |

| 6  | GND      | 26 | MOSI   | 46 | VDDIO  | 66 | VDDOUT AN |

| 7  | CLKEA    | 27 | MISO   | 47 | GND    | 67 | AGND      |

| 8  | GND      | 28 | VDDIO  | 48 | VDDOUT | 68 | VRP       |

| 9  | CLKEB    | 29 | GND    | 49 | TXRX0  | 69 | VRM       |

| 10 | VDDIO    | 30 | EMIT0  | 50 | TXRX1  | 70 | VRC       |

| 11 | GND      | 31 | EMIT1  | 51 | GND    | 71 | VDDIN AN  |

| 12 | VDDPLL   | 32 | EMIT2  | 52 | AGC2   | 72 | AGND      |

| 13 | GND      | 33 | EMIT3  | 53 | AGC5   | 73 | AGND      |

| 14 | VDDIN    | 34 | VDDIO  | 54 | AGC1   | 74 | VDDIN AN  |

| 15 | VDDIN    | 35 | GND    | 55 | AGC4   | 75 | GND       |

| 16 | GND      | 36 | EMIT4  | 56 | AGC0   | 76 | VDDIO     |

| 17 | VDDOUT   | 37 | EMIT5  | 57 | AGC3   | 77 | VZ CROSS  |

| 18 | GND      | 38 | EMIT6  | 58 | VDDIO  | 78 | NC        |

| 19 | NC       | 39 | EMIT7  | 59 | GND    | 79 | NC        |

| 20 | SRST     | 40 | VDDIO  | 60 | EINT   | 80 | NC        |

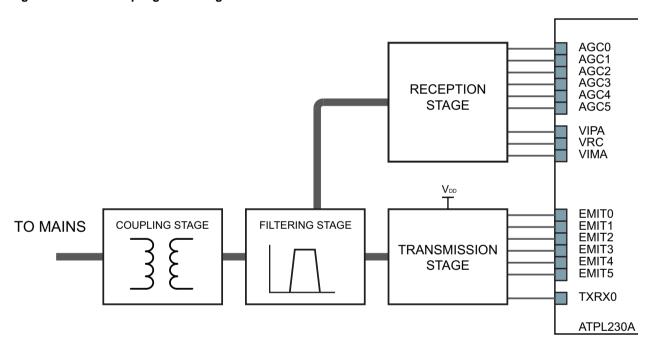

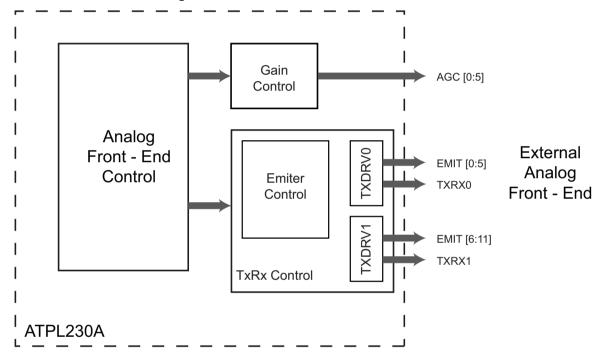

## 5. Analog Front-End

### 5.1 PLC coupling circuitry description

Atmel PLC coupling reference designs have been designed to achieve high performance, low cost and simplicity.

With these values on mind, Atmel has developed a set of PLC couplings covering frequencies up to 472 kHz compliant with different applicable regulations.

Atmel PLC technology is purely digital and does not require external DAC/ADC, thus simplifying the external required circuitry. Generally Atmel PLC coupling reference designs make use of few passive components plus a Class D amplification stage for transmission.

All PLC coupling reference designs are generally composed by the same sub-circuits:

- Transmission Stage

- Reception Stage

- Filtering Stage

- Coupling Stage

Figure 5-1. PLC coupling block diagram

A particular reference design can contain more than one sub-circuit of the same kind (i.e.: two transmission stages).

### 5.1.1 Transmission Stage

The transmission stage adapts the EMIT signals and amplifies them if required. It can be composed by:

- Driver: A group of resistors which adapt the EMIT signals to either control the Class-D amplifier or to be filtered by the next stage.

- Amplifier: If required, a Class-D amplifier which generates a square waveform from 0 to V<sub>DD</sub> is included.

- Bias and protection: A couple of resistors and a couple of Schottky barrier diodes provide a DC component and provide protection from received disturbances.

Transmission stage shall be always followed by a filtering stage.

### 5.1.2 Filtering Stage

The filtering stage is composed by band-pass filters which have been designed to achieve high performance in field deployments complying at the same time with the proper normative and standards.

The in-band flat response filtering stage does not distort the injected signal, reduces spurious emission to the limits set by the corresponding regulation and blocks potential interferences from other transmission channels.

The filtering stage has three aims:

- Band-pass filtering of high frequency components of the square waveform generated by the transmission stage

- Adapt Input/Output impedances for optimal reception/transmission. This is controlled by TXRX signals

- In some cases, Band-pass filtering for received signals

When the system is intended to be connected to a physical channel with high voltage or which is not electrically referenced to the same point then the filtering stage must be always followed by a coupling stage.

#### 5.1.3 Coupling Stage

The coupling stage blocks the DC component of the line to/from which the signal is injected/received (i.e.: 50/60 Hz of the mains). This is carried out by a high voltage capacitor.

Coupling stage could also electrically isolate the coupling circuitry from the external world by means of a 1:1 transformer.

#### 5.1.4 Reception Stage

The reception stage adapts the received analog signal to be properly captured by the ATPL230A internal reception chain. Reception circuit is independent of the PLC channel which is being used. It basically consists of:

- Anti aliasing filter (RC Filter)

- Automatic Gain Control (AGC) circuit

- Driver of the internal ADC

The AGC circuit avoids distortion on the received signal that may arise when the input signal is high enough to polarize the protective diodes in direct region.

The driver to the internal ADC comprises a couple of resistors and a couple of capacitors. This driver provides a DC component and adapts the received signal to be properly converted by the internal reception chain.

### 5.1.5 Generic PLC Coupling

Please consider that this is a generic PLC Coupling design for a particular application please refer to Atmel doc43052 "PLC Coupling Reference Designs".

Figure 5-2. PLC Coupling block diagram detailed

# 5.2 ATPLCOUP reference designs

Atmel provides PLC coupling reference designs for different applications and frequency bands up to 500 kHz. Please refer to Atmel doc43052 "PLC Coupling Reference Designs" for a detailed description.

### 5.3 Zero-crossing detection

#### 5.3.1 Overview

Zero Crossing Detector block works predicting future zero crossings of the Mains signal in function of its past zero crossings. To achieve this, the system embeds a configurable Input Signal Management (ISM) block and a PLL, both of which manage Zero Crossing Detector Input Signal to calculate Zero Crossing Output Flag. The zero-cross detection of waves of 50 Hz and 60 Hz with ±10% of error is supported.

The PLL block interprets its input signal such a way that it indicates a zero cross in the middle of a positive pulse. It is important to note that depending on the external circuit implementing the Zero Crossing Detector Input Signal this interpretation is not always correct. Thus, for some cases it is required to transform the Input Signal in a signal where the middle of a positive pulse corresponds to a truly zero cross. This transformation is implemented through the Input Signal Management (ISM) block, configured by MODE INV and MODE REP fields in ZC CONFIG register.

Zero Crossing Detector Input Signal (VZ CROSS) must fulfil some requirements. The first requirement is that VZ CROSS signal must be a pulse train with a duty cycle being >60% or <40% (polarity is configurable). In addition, if we have to detect ascent or descent zero-crossing, the Zero Crossing Detector Input Signal period must be equal than the period of the wave we need to obtain zero-crossing. Ascent and descent Zero Crossing Detection are configured by setting MODE MUX and MODE ASC fields in ZC CONFIG register.

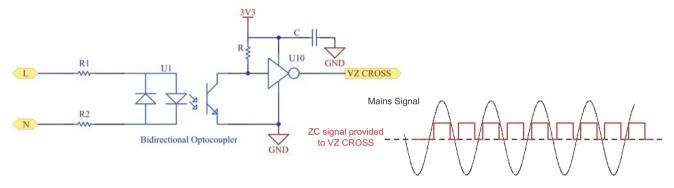

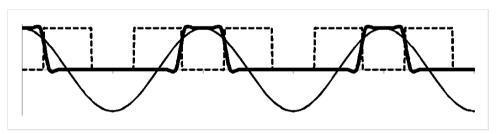

Figure 5-3. Typical circuit, using a bidirectional optocoupler and a Schmitt trigger

The input signal "VZ CROSS" (wider line) generated by this circuit for Zero Cross Detection of the wave "L"-"N" (finer line) is plotted in next figure. The digital signal at output of Input Signal Management (ISM) is plotted in Figure 5-4.

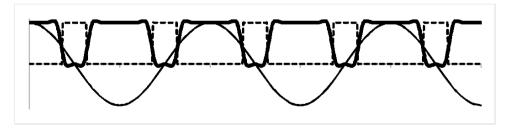

Figure 5-4. Digital signal (dashed line) at output of Input Signal Management (ISM) internal block

For this circuit, Zero Cross Internal registers should be configured this way:

```

ZC_CONFIG.MODE_MUX = '0'

ZC_CONFIG.MODE_ASC = '0'

ZC_CONFIG.MODE_INV = '1'

ZC_CONFIG.MODE_REP = '0'

ZC_FILTER.ZC_FILTER_BP = '0'

```

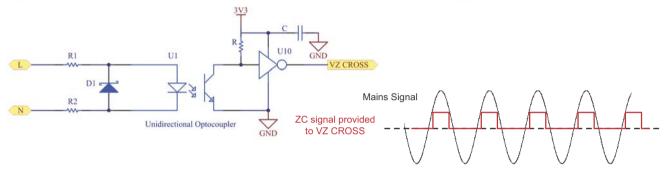

Some situations (for example in some protocols needing to differentiate rising/falling edges in mains signal) could require only ascent (or descent) mains signal zero-crossings to be detected. When we have to detect ascent or descent Zero-Cross of the wave (finer line), the circuit should generate an input signal "VZ CROSS" (wider line) with the same period, as specified in next figure. This could be easily implemented by using an unidirectional optocoupler or a Zener diode topology in the external circuitry.

Figure 5-5. Typical circuit, using a unidirectional optocoupler and a Schmitt trigger

The digital signal at output of Input Signal Management (ISM) is plotted in Figure 5-6.

Figure 5-6. Digital signal (dashed line) at output of Input Signal Management (ISM) internal block

For this case, Zero Cross Internal registers should be configured this way:

```

ZC_CONFIG.MODE_MUX = '1'

ZC_CONFIG.MODE_ASC = '0'(ascent) or '1'(descent)

ZC_CONFIG.MODE_INV = '1'

ZC_CONFIG.MODE_REP = '1'

ZC_FILTER.ZC_FILTER_BP = '0'

```

See register description in Section 9.3.7.2 "Zero Crossing Configuration Register" and Section 9.3.7.3 "Zero Crossing Filter Register".

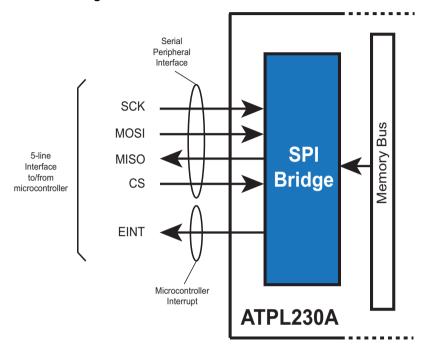

### 6. SPI Controller

ATPL230A has been conceived to be easily managed by an external microcontroller through a 5-line interface. This interface is comprised of a 4-line standard Serial Peripheral Interface (SPI) and an additional line used as interrupt from the ATPL230A to the external microcontroller. A diagram is shown below.

Figure 6-1. SPI Controller Block Diagram

By means of this SPI interface, an external microcontroller can access the ATPL230A and can carry out "write", "write\_rep", "read" and "mask" operations. All the "Peripheral Registers" in ATPL230A are reachable via the SPI interface, thus the microcontroller can fully manage and control the ATPL230A (PHY layer, MAC co-processing, etc).

### 6.1 Serial Peripheral Interface

The Serial Peripheral Interface Bus or SPI bus is a synchronous serial data link standard. Devices communicate in master/slave mode where the master device initiates the data frame. Multiple slave devices are allowed with individual slave select (chip select) lines.

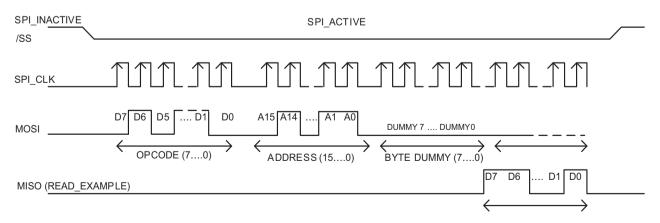

Figure 6-2. SPI Communication Example in ATPL230A

The ATPL230A SPI allows an external device (working as a master), to communicate with the ATPL230A (working as a slave). Below is a brief description of the SPI signals:

• CS, Chip Select (pin no.24): This input enables/disables the slave SPI. The ATPL230A is configured to work always as a slave. When disabled (CS pin is tied high), the other SPI signals (SCK, MOSI and MISO) are not taken into account.

CS = '0': SPI enabled.

CS = '1': SPI disabled.

SCK, Serial Peripheral Interface Clock (pin no.25): In reception (master slave), data is read from MOSI line

in the rising edge of the SPI clock. In transmission (slave master), data is released to MISO in the falling edge

of the SPI clock.

It is recommended not to work with clock frequencies above 10MHz.

This input only will be taken into account when CS='0'.

MOSI, Master Out Slave In (pin no.26): MOSI is the slave's data input line. Data is read from MOSI line in the rising edge of SCK.

This input only will be taken into account when CS='0'.

MISO, Master In Slave Out (pin no.27): MISO is the slave's data output line. Data is released to MISO in the falling edge of SCK.

Furthermore, ATPL230A SPI bridge uses an additional line to send interrupts to the host CPU:

EINT (pin no.60): This signal is an interrupt from ATPL230A PHY layer to the microcontroller.

In reception, every time a PLC message is received, the PHY Layer generates two interrupts. One of them when the physical header is correctly received (two first symbols), and the other one when the message is completely received.

In transmission, an interrupt will be generated every time a complete message has been sent.

This signal is low level active.

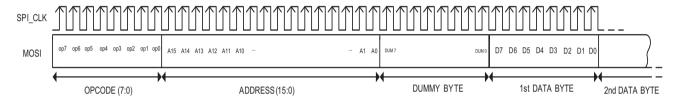

### 6.2 SPI Operation

When establishing a SPI communication (CS line is set to '0' by the master), the first byte sent through MOSI line corresponds to the operation code. Four different operation types are defined over ATPL230A SPI. The operation codes are shown in the following table:

Table 6-1. Operation Codes

| Operation | Mask type | OpCode |

|-----------|-----------|--------|

| Read      |           | 0x63   |

| Write     |           | 0x2A   |

|           | AND       | 0x4C   |

| Mask      | OR        | 0x71   |

|           | XOR       | 0x6D   |

| Write_rep |           | 0x1E   |

Following the operation code, the second and third bytes correspond to the SRAM address (16-bit address). Depending on the operation code, the master will "read data from"/"write data to"/"mask data in"/"write some data to" that address.

After the address, a dummy byte is sent.

Following the dummy byte, n data bytes (where  $n \ge 1$ ) are sent/received:

- If the operation code corresponds to a write operation in memory, the first data byte will be written in the specified address. If more data bytes are sent, they will be written in subsequent memory positions.

- If the operation code corresponds to a read operation from memory, the ATPL230A will output the data byte in MISO line. If the master continues sending SCK cycles, subsequent memory positions will be written in MISO line by the slave.

- If the operation code corresponds to a mask operation (AND, OR, XOR), the master will send the byte mask

that have to be applied to the byte located at the specified address memory. If the master continues sending

bytes, they will be applied as masks to the bytes stored in subsequent memory positions.

- If the operation code corresponds to a write\_rep operation in memory, the dummy byte is changed by a number between 0x00 and 0xFF, called OFFSET\_ADDRESS. Data bytes will be written from ADDRESS to ADDRESS+OFFSET\_ADDRESS. For example, if OFFSET\_ADDRESS = 0x04, the five first data bytes will be written between ADDRESS and ADDRESS+4, and then, the sixth data byte, will be written in ADDRESS, the seventh in ADDRESS+1, and so on. It is used to fill the some memories in PHY Layer (Chirp, Angle and IIR).

Bytes will be always sent with the most significant bit first.

Figure 6-3. SPI Frame Example

# 7. Peripheral Registers

A total of 768 bytes are reserved on-chip to allocate the system peripheral registers.

A detailed description of each peripheral register can be found in its corresponding section. On the next pages, there is a list of all of them.

Table 7-1. Register Mapping

| Address         | Register                     | Name                  | Access     | Reset      |

|-----------------|------------------------------|-----------------------|------------|------------|

| 0xFD00 - 0xFD03 |                              | TXRXBUF_EMITIME_TX0   | Read/Write | 0x0000     |

| 0xFD04 - 0xFD07 | TV Time Degisters            | TXRXBUF_EMITIME_TX1   | Read/Write | 0x0000     |

| 0xFD08 - 0xFD0B | TX Time Registers            | TXRXBUF_EMITIME_TX2   | Read/Write | 0x0000     |

| 0xFD0C - 0xFD0F |                              | TXRXBUF_EMITIME_TX3   | Read/Write | 0x0000     |

| 0xFD10 - 0xFD11 |                              | TXRXBUF_TXRX_TA_TX0   | Read/Write | 0x0000     |

| 0xFD12 - 0xFD13 | TX Post-activation Time      | TXRXBUF_TXRX_TA_TX1   | Read/Write | 0x0000     |

| 0xFD14 - 0xFD15 | TxRx Registers               | TXRXBUF_TXRX_TA_TX2   | Read/Write | 0x0000     |

| 0xFD16 - 0xFD17 |                              | TXRXBUF_TXRX_TA_TX3   | Read/Write | 0x0000     |

| 0xFD18 - 0xFD19 |                              | TXRXBUF_TXRX_TB_TX0   | Read/Write | 0x0000     |

| 0xFD1A - 0xFD1B | TX Pre-activation Time TxRx  | TXRXBUF_TXRX_TB_TX1   | Read/Write | 0x0000     |

| 0xFD1C - 0xFD1D | Registers                    | TXRXBUF_TXRX_TB_TX2   | Read/Write | 0x0000     |

| 0xFD1E - 0xFD1F |                              | TXRXBUF_TXRX_TB_TX3   | Read/Write | 0x0000     |

| 0xFD20          |                              | TXRXBUF_GLBL_AMP_TX0  | Read/Write | 0xFF       |

| 0xFD21          | Clobal Amplitude Degisters   | TXRXBUF_GLBL_AMP_TX1  | Read/Write | 0xFF       |

| 0xFD22          | Global Amplitude Registers   | TXRXBUF_GLBL_AMP_TX2  | Read/Write | 0xFF       |

| 0xFD23          |                              | TXRXBUF_GLBL_AMP_TX3  | Read/Write | 0xFF       |

| 0xFD24          |                              | TXRXBUF_SGNL_AMP_TX0  | Read/Write | 0x60       |

| 0xFD25          | Cianal Amenituda Daniatana   | TXRXBUF_SGNL_AMP_TX1  | Read/Write | 0x60       |

| 0xFD26          | Signal Amplitude Registers   | TXRXBUF_SGNL_AMP_TX2  | Read/Write | 0x60       |

| 0xFD27          |                              | TXRXBUF_SGNL_AMP_TX3  | Read/Write | 0x60       |

| 0xFD28          |                              | TXRXBUF_CHIRP_AMP_TX0 | Read/Write | 0x60       |

| 0xFD29          | Chirp Amplitude Degisters    | TXRXBUF_CHIRP_AMP_TX1 | Read/Write | 0x60       |

| 0xFD2A          | Chirp Amplitude Registers    | TXRXBUF_CHIRP_AMP_TX2 | Read/Write | 0x60       |

| 0xFD2B          |                              | TXRXBUF_CHIRP_AMP_TX3 | Read/Write | 0x60       |

| 0xFD2C - 0xFD2F |                              | TXRXBUF_TIMEOUT_TX0   | Read/Write | 0x000124F8 |

| 0xFD30 - 0xFD33 | TV Timequit Degisters        | TXRXBUF_TIMEOUT_TX1   | Read/Write | 0x000124F8 |

| 0xFD34 - 0xFD37 | TX Timeout Registers         | TXRXBUF_TIMEOUT_TX2   | Read/Write | 0x000124F8 |

| 0xFD38 - 0xFD3B |                              | TXRXBUF_TIMEOUT_TX3   | Read/Write | 0x000124F8 |

| 0xFD3C          |                              | TXRXBUF_TXCONF_TX0    | Read/Write | 0xA0       |

| 0xFD3D          | TV Configuration Desigtan    | TXRXBUF_TXCONF_TX1    | Read/Write | 0xA0       |

| 0xFD3E          | TX Configuration Registers   | TXRXBUF_TXCONF_TX2    | Read/Write | 0xA0       |

| 0xFD3F          |                              | TXRXBUF_TXCONF_TX3    | Read/Write | 0xA0       |

| 0xFD40 - 0xFD41 |                              | TXRXBUF_INITAD_TX0    | Read/Write | 0x0000     |

| 0xFD42 - 0xFD43 | TX Initial Address Registers | TXRXBUF_INITAD_TX1    | Read/Write | 0x0000     |

| 0xFD44 - 0xFD45 |                              | TXRXBUF_INITAD_TX2    | Read/Write | 0x0000     |

| 0xFD46 - 0xFD47 |                              | TXRXBUF_INITAD_TX3    | Read/Write | 0x0000     |

Table 7-1. Register Mapping

| Address         | Register               | Name                    | Access    | Reset  |

|-----------------|------------------------|-------------------------|-----------|--------|

| 0xFD48 - 0xFD49 |                        | -                       | -         | 0x0000 |

| 0xFD4A - 0xFD4B | Reserved               | -                       | -         | 0x0000 |

| 0xFD4C - 0xFD4D |                        | -                       | -         | 0x0000 |

| 0xFD4E - 0xFD4F |                        | -                       | -         | 0x0000 |

| 0xFD50 - 0xFD51 | TX Result Register     | TXRXBUF_RESULT_TX       | Read-only | 0x1111 |

| 0xFD52          | TX Interrupts Register | TXRXBUF_TX_INT          | Read-only | 0x00   |

| 0xFD53          |                        | -                       | -         | 0x00   |

| 0xFD54          | Reserved               | -                       | -         | 0x00   |

| 0xFD55          | Reserved               | -                       | -         | 0x00   |

| 0xFD56          |                        | -                       | -         | 0x00   |

| 0xFD57          |                        | TXRXBUF_BERSOFT_AVG_RX0 | Read-only | 0x00   |

| 0xFD58          | BER SOFT Average Error | TXRXBUF_BERSOFT_AVG_RX1 | Read-only | 0x00   |

| 0xFD59          | Registers              | TXRXBUF_BERSOFT_AVG_RX2 | Read-only | 0x00   |

| 0xFD5A          |                        | TXRXBUF_BERSOFT_AVG_RX3 | Read-only | 0x00   |

| 0xFD5B          |                        | TXRXBUF_BERSOFT_MAX_RX0 | Read-only | 0x00   |

| 0xFD5C          | BER SOFT Maximum Error | TXRXBUF_BERSOFT_MAX_RX1 | Read-only | 0x00   |

| 0xFD5D          | Registers              | TXRXBUF_BERSOFT_MAX_RX2 | Read-only | 0x00   |

| 0xFD5E          |                        | TXRXBUF_BERSOFT_MAX_RX3 | Read-only | 0x00   |

| 0xFD5F          |                        | -                       | -         | 0x00   |

| 0xFD60          |                        | -                       | -         | 0x00   |

| 0xFD61          | Reserved               | -                       | -         | 0x00   |

| 0xFD62          |                        | -                       | -         | 0x00   |

| 0xFD63          |                        | TXRXBUF_BERHARD_AVG_RX0 | Read-only | 0x00   |

| 0xFD64          | BER HARD Average Error | TXRXBUF_BERHARD_AVG_RX1 | Read-only | 0x00   |

| 0xFD65          | Registers              | TXRXBUF_BERHARD_AVG_RX2 | Read-only | 0x00   |

| 0xFD66          |                        | TXRXBUF_BERHARD_AVG_RX3 | Read-only | 0x00   |

| 0xFD67          |                        | TXRXBUF_BERHARD_MAX_RX0 | Read-only | 0x00   |

| 0xFD68          | BER HARD Maximum Error | TXRXBUF_BERHARD_MAX_RX1 | Read-only | 0x00   |

| 0xFD69          | Registers              | TXRXBUF_BERHARD_MAX_RX2 | Read-only | 0x00   |

| 0xFD6A          | 1                      | TXRXBUF_BERHARD_MAX_RX3 | Read-only | 0x00   |

| 0xFD6B          |                        | TXRXBUF_RSSIMIN_RX0     | Read-only | 0x00   |

| 0xFD6C          |                        | TXRXBUF_RSSIMIN_RX1     | Read-only | 0x00   |

| 0xFD6D          | Minimum RSSI Registers | TXRXBUF_RSSIMIN_RX2     | Read-only | 0x00   |

| 0xFD6E          | 1                      | TXRXBUF_RSSIMIN_RX3     | Read-only | 0x00   |

| 0xFD6F          |                        | TXRXBUF_RSSIAVG_RX0     | Read-only | 0x00   |

| 0xFD70          | 1                      | TXRXBUF_RSSIAVG_RX1     | Read-only | 0x00   |

| 0xFD71          | Average RSSI Registers | TXRXBUF_RSSIAVG_RX2     | Read-only | 0x00   |

| 0xFD72          | 1                      | TXRXBUF RSSIAVG RX3     | Read-only | 0x00   |

| 0xFD73          |                        | TXRXBUF_RSSIMAX_RX0     | Read-only | 0x00   |

| 0xFD74          | -                      | TXRXBUF_RSSIMAX_RX1     | Read-only | 0x00   |

| 0xFD75          | Maximum RSSI Registers | TXRXBUF_RSSIMAX_RX2     | Read-only | 0x00   |

| 0xFD76          |                        | TXRXBUF_RSSIMAX_RX3     | Read-only | 0x00   |

Table 7-1. Register Mapping

| Address         | Register                   | Name                    | Access     | Reset  |

|-----------------|----------------------------|-------------------------|------------|--------|

| 0xFD77          |                            | TXRXBUF_CINRMIN_RX0     | Read-only  | 0x00   |

| 0xFD78          | Minimum CIND Degisters     | TXRXBUF_CINRMIN_RX1     | Read-only  | 0x00   |

| 0xFD79          | - Minimum CINR Registers   | TXRXBUF_CINRMIN_RX2     | Read-only  | 0x00   |

| 0xFD7A          |                            | TXRXBUF_CINRMIN_RX3     | Read-only  | 0x00   |

| 0xFD7B          |                            | TXRXBUF_CINRAVG_RX0     | Read-only  | 0x00   |

| 0xFD7C          | Average CIND Decistors     | TXRXBUF_CINRAVG_RX1     | Read-only  | 0x00   |

| 0xFD7D          | - Average CINR Registers   | TXRXBUF_CINRAVG_RX2     | Read-only  | 0x00   |

| 0xFD7E          | -                          | TXRXBUF_CINRAVG_RX3     | Read-only  | 0x00   |

| 0xFD7F          |                            | TXRXBUF_CINRMAX_RX0     | Read-only  | 0x00   |

| 0xFD80          | Mavinous CIND Desisters    | TXRXBUF_CINRMAX_RX1     | Read-only  | 0x00   |

| 0xFD81          | - Maximum CINR Registers   | TXRXBUF_CINRMAX_RX2     | Read-only  | 0x00   |

| 0xFD82          | -                          | TXRXBUF_CINRMAX_RX3     | Read-only  | 0x00   |

| 0xFD83 - 0xFD86 |                            | TXRXBUF_RECTIME_RX0     | Read-only  | 0x0000 |

| 0xFD87 - 0xFD8A | DV Time Decistans          | TXRXBUF_RECTIME_RX1     | Read-only  | 0x0000 |

| 0xFD8B - 0xFD8E | - RX Time Registers        | TXRXBUF_RECTIME_RX2     | Read-only  | 0x0000 |

| 0xFD8F - 0xFD92 |                            | TXRXBUF_RECTIME_RX3     | Read-only  | 0x0000 |

| 0xFD93 - 0xFD96 |                            | TXRXBUF_ZCT_RX0         | Read-only  | 0x0000 |

| 0xFD97 - 0xFD9A | Zava Crasa Timas Danistana | TXRXBUF_ZCT_RX1         | Read-only  | 0x0000 |

| 0xFD9B - 0xFD9E | Zero-Cross Time Registers  | TXRXBUF_ZCT_RX2         | Read-only  | 0x0000 |

| 0xFD9F - 0xFDA2 |                            | TXRXBUF_ZCT_RX3         | Read-only  | 0x0000 |

| 0xFDA3 - 0xFDA4 |                            | TXRXBUF_EVM_HD_RX0      | Read-only  | 0x0000 |

| 0xFDA5 - 0xFDA6 | Hooder EVM Degisters       | TXRXBUF_EVM_HD_RX1      | Read-only  | 0x0000 |

| 0xFDA7 - 0xFDA8 | Header EVM Registers       | TXRXBUF_EVM_HD_RX2      | Read-only  | 0x0000 |

| 0xFDA9 - 0xFDAA |                            | TXRXBUF_EVM_HD_RX3      | Read-only  | 0x0000 |

| 0xFDAB - 0xFDAC |                            | TXRXBUF_EVM_PYLD_RX0    | Read-only  | 0x0000 |

| 0xFDAD - 0xFDAE | Dayload EVM Pogistors      | TXRXBUF_EVM_PYLD_RX1    | Read-only  | 0x0000 |

| 0xFDAF - 0xFDB0 | Payload EVM Registers      | TXRXBUF_EVM_PYLD_RX2    | Read-only  | 0x0000 |

| 0xFDB1 - 0xFDB2 |                            | TXRXBUF_EVM_PYLD_RX3    | Read-only  | 0x0000 |

| 0xFDB3 - 0xFDB6 |                            | TXRXBUF_EVM_HDACUM_RX0  | Read-only  | 0x0000 |

| 0xFDB7 - 0xFDBA | Accumulated Header EVM     | TXRXBUF_EVM_HDACUM_RX1  | Read-only  | 0x0000 |

| 0xFDBB - 0xFDBE | Registers                  | TXRXBUF_EVM_HDACUM_RX2  | Read-only  | 0x0000 |

| 0xFDBF - 0xFDC2 |                            | TXRXBUF_EVM_HDACUM_RX3  | Read-only  | 0x0000 |

| 0xFDC3 - 0xFDC6 |                            | TXRXBUF_EVM_PYLACUM_RX0 | Read-only  | 0x0000 |

| 0xFDC7 - 0xFDCA | Accumulated Payload EVM    | TXRXBUF_EVM_PYLACUM_RX1 | Read-only  | 0x0000 |

| 0xFDCB - 0xFDCE | Registers                  | TXRXBUF_EVM_PYLACUM_RX2 | Read-only  | 0x0000 |

| 0xFDCF - 0xFDD2 |                            | TXRXBUF_EVM_PYLACUM_RX3 | Read-only  | 0x0000 |

| 0xFDD3          | Buffer Selection Register  | TXRXBUF_SELECT_BUFF_RX  | Read/Write | 0x00   |

| 0xFDD4          | RX Interrupts Register     | TXRXBUF_RX_INT          | Read/Write | 0x00   |

| 0xFDD5          | RX Configuration Register  | TXRXBUF_RXCONF          | Read/Write | 0x02   |

Table 7-1. Register Mapping

| Address         | Register                            | Name                     | Access     | Reset  |

|-----------------|-------------------------------------|--------------------------|------------|--------|

| 0xFDD6 - 0xFDD7 |                                     | TXRXBUF_INITAD_RX0       | Read/Write | 0x0000 |

| 0xFDD8 - 0xFDD9 | RX Initial Address Registers        | TXRXBUF_INITAD_RX1       | Read/Write | 0x0000 |

| 0xFDDA - 0xFDDB | NA IIIIIIai Audiess Registers       | TXRXBUF_INITAD_RX2       | Read/Write | 0x0000 |

| 0xFDDC - 0xFDDD |                                     | TXRXBUF_INITAD_RX3       | Read/Write | 0x0000 |

| 0xFDDE - 0xFDE1 | Reserved                            | -                        | -          | 0x0000 |

| 0xFDE2 - 0xFDE5 | Reserved                            | -                        | -          | 0x0000 |

| 0xFDE6          |                                     | -                        | -          | 0x00   |

| 0xFDE7          | Reserved                            | -                        | -          | 0x00   |

| 0xFDE8          |                                     | -                        | -          | 0x00   |

| 0xFDE9          |                                     | -                        | -          | 0x00   |

| 0xFDEA - 0xFDEB |                                     | -                        | -          | 0x0000 |

| 0xFDEC - 0xFDED | Reserved                            | -                        | -          | 0x0000 |

| 0xFDEE - 0xFDEF |                                     | -                        | -          | 0x0000 |

| 0xFDF0 - 0xFDF1 |                                     | -                        | -          | 0x0000 |

| 0xFDF2          | Robust TX Control Register          | TXRXBUF_TXCONF_ROBO_CTL  | Read/Write | 0x00   |

| 0xFDF3          | Robust RX Mode Register             | TXRXBUF_RXCONF_ROBO_MODE | Read-only  | 0x00   |

| 0xFDF4 - 0xFDF7 | Reserved                            | -                        | -          | 0x0000 |

| 0xFDF8 - 0xFDF9 | Reserved                            | -                        | -          | 0x0000 |

| 0xFDFA          | Reserved                            | -                        | -          | 0xE0   |

| 0xFDFB          | Branch Selection Register           | TXRXBUF_TXCONF_SELBRANCH | Read/Write | 0x00   |

| 0xFDFC          | Reserved                            | -                        | -          | 0x00   |

| 0xFDFD          | Reserved                            | -                        | -          | 0x00   |

| 0xFDFE          | Reserved                            | -                        | -          | 0x00   |

| 0xFDFF          | Reserved                            | -                        | -          | 0x00   |

| 0xFE2A          | PHY Layer Special Function Register | PHY_SFR                  | Read/Write | 0x87   |

| 0xFE2C          | System Configuration<br>Register    | SYS_CONFIG               | Read/Write | 0x04   |

| 0xFE30          |                                     | -                        | -          | 0x00   |

| 0xFE31          |                                     | -                        | -          | 0x00   |

| 0xFE32          |                                     | -                        | -          | 0x00   |

| 0xFE33          | Doggrand                            | -                        | -          | 0x00   |

| 0xFE34          | Reserved                            | -                        | -          | 0x00   |

| 0xFE35          |                                     | -                        | -          | 0x00   |

| 0xFE36          |                                     | -                        | -          | 0x00   |

| 0xFE37          |                                     | -                        | -          | 0x00   |

| 0xFE38          |                                     | -                        | -          | 0x40   |

| 0xFE39          |                                     | -                        | -          | 0x40   |

| 0xFE3A          | Reserved                            | -                        | -          | 0x40   |

| 0xFE3B          |                                     | -                        | -          | 0x40   |

Table 7-1. Register Mapping

| Address         | Register                            | Name             | Access     | Reset      |

|-----------------|-------------------------------------|------------------|------------|------------|

| 0xFE3C          |                                     | -                | -          | 0x10       |

| 0xFE3D          | Decembed                            | -                | -          | 0x10       |

| 0xFE3E          | Reserved                            | -                | -          | 0x10       |

| 0xFE3F          |                                     | -                | -          | 0x10       |

| 0xFE47 - 0xFE4A | PHY Layer Timer Register            | TIMER_BEACON_REF | Read-only  | 0x0000     |

| 0xFE53 - 0xFE55 | Reserved                            | -                | -          | 0x000200   |

| 0xFE57          | Reserved                            | -                | -          | 0x1E       |

| 0xFE5C          |                                     | -                | -          | 0x0C       |

| 0xFE5D          | Reserved                            | -                | -          | 0x18       |

| 0xFE5F          | Reserved                            | -                | -          | 0x26       |

| 0xFE60          | -                                   | -                | -          | 0x2B       |

| 0xFE62 - 0xFE67 | Sub Network Address<br>Register     | SNA              | Read/Write | 0x0000     |

| 0xFE68          | Reserved                            | -                | -          | 0x5F       |

| 0xFE69 - 0xFE6A |                                     | -                | -          | 0xFFFF     |

| 0xFE6B - 0xFE6C |                                     | -                | -          | 0xFFFF     |

| 0xFE6D - 0xFE6E | Reserved                            | -                | -          | 0xFFFF     |

| 0xFE6F - 0xFE70 | -                                   | -                | -          | 0xFFFF     |

| 0xFE71 - 0xFE72 |                                     | -                | -          | 0xFFFF     |

| 0xFE73          | Reserved                            | -                | -          | 0x56       |

| 0xFE7D - 0xFE7E | Reserved                            | -                | -          | 0x814C     |

| 0xFE7F          | Reserved                            | -                | -          | 0x00       |

| 0xFE80 - 0xFE81 | Reserved                            | -                | -          | 0x0000     |

| 0xFE8F          | Reserved                            | -                | -          | 0x03       |

| 0xFE90          | TXRX Polarity Selector<br>Register  | AFE_CTL          | Read/Write | 0x00       |

| 0xFE91          | Reserved                            | -                | -          | 0x1E       |

| 0xFE92          | Reserved                            | -                | -          | 0x28       |

| 0xFE94          | PHY Layer Error Counter<br>Register | PHY_ERRORS       | Read/Write | 0x00       |

| 0xFE9D          | Reserved                            | -                | -          | 0x21       |

| 0xFE9E          | Reserved                            | -                | -          | 0x05       |

| 0xFE9F          | Reserved                            | -                | -          | 0x60       |

| 0xFEA0          | Reserved                            | -                | -          | 0x60       |

| 0xFEA1          | Reserved                            | -                | -          | 0x60       |

| 0xFEA2          | Reserved                            | -                | -          | 0x60       |

| 0xFEA3 - 0xFEA6 | Reserved                            | -                | -          | 0x77777777 |

| 0xFEAB - 0xFEAC | Reserved                            | -                | -          | 0x5508     |

| 0xFEAD - 0xFEAE | Reserved                            | -                | -          | 0x3C20     |

| 0xFEAF          | Reserved                            | -                | -          | 0x00       |

| 0xFEB0          | Reserved                            | -                | -          | 0x00       |

| 0xFEB4          | Reserved                            | -                | -          | 0x00       |

| 0xFEB5 - 0xFEB6 | Reserved                            | -                | -          | 0x0066     |

Table 7-1. Register Mapping

| Address         | Register                              | Name                  | Access     | Reset  |

|-----------------|---------------------------------------|-----------------------|------------|--------|

| 0xFEB7          | Reserved                              | -                     |            | 0x00   |

| 0xFEBA - 0xFEBB | CRC32 Errors Counter<br>Register      | ERR_CRC32_MAC         | Read-only  | 0x0000 |

| 0xFEBC - 0xFEBD | CRC8 Errors Counter<br>Register       | ERR_CRC8_MAC          | Read-only  | 0x0000 |

| 0xFEC0 - 0xFEC1 | CRC8 HD Errors Counter<br>Register    | ERR_CRC8_MAC_HD       | Read-only  | 0x0000 |

| 0xFEC2 - 0xFEC3 | CRC8 PHY Errors Counter<br>Register   | ERR_CRC8_PHY          | Read-only  | 0x0000 |

| 0xFEC4          | False Positive Configuration Register | FALSE_POSITIVE_CONFIG | Read/Write | 0x10   |

| 0xFEC5 - 0xFEC6 | False Positive Counter<br>Register    | FALSE_POSITIVE        | Read-only  | 0x0000 |

| 0xFEC8          | Reserved                              | -                     | -          | 0x3F   |

| 0xFEC9          | Reserved                              | -                     | -          | 0x3F   |

| 0xFECA          | Reserved                              | -                     | -          | 0x3F   |

| 0xFECB          | Reserved                              | -                     | -          | 0x3F   |

| 0xFECC          | Reserved                              | -                     | -          | 0x3F   |

| 0xFECD          | Reserved                              | -                     | -          | 0x3F   |

| 0xFECE - 0xFECF | Reserved                              | -                     | -          | 0x0000 |

| 0xFED3          | Reserved                              | -                     | -          | 0x40   |

| 0xFED5 - 0xFED6 | Reserved                              | -                     | -          | 0x0000 |

| 0xFEDB          | Reserved                              | -                     | -          | 0x00   |

| 0xFEDC - 0xFEDF | Reserved                              | -                     | -          | 0x0000 |

| 0xFEE0          | Reserved                              | -                     | -          | 0x02   |

| 0xFEE4 - 0xFEE5 | Reserved                              | -                     | -          | 0x0000 |

| 0xFEE6 - 0xFEE7 | Reserved                              | -                     | -          | 0x0000 |

| 0xFEE8          | Reserved                              | -                     | -          | 0x00   |

| 0xFEE9          | Reserved                              | -                     | -          | 0xFF   |

| 0xFEEA          | Reserved                              | -                     | -          | 0x04   |

| 0xFEEB          | Reserved                              | -                     | -          | 0x08   |

| 0xFEEC          | Reserved                              | -                     | -          | 0x0C   |

| 0xFEED          | Reserved                              | -                     | -          | 0x14   |

| 0xFEEE          | Reserved                              | -                     | -          | 0x00   |

| 0xFEEF          | Reserved                              | -                     | -          | 0x03   |

| 0xFEF0          | Reserved                              | -                     | -          | 0x00   |

| 0xFEF1          | Reserved                              | -                     | -          | 0x17   |

| 0xFEF2          | Reserved                              | -                     | -          | 0x18   |

| 0xFEF3          | Reserved                              | -                     | -          | 0x23   |

| 0xFEF4          | CRC PRIMEPLUS Configuration Register  | PRIMEPLUS_CRC_CONFIG  | Read/Write | 0x14   |

| 0xFEF5 - 0xFEF6 | CRC PRIMEPLUS<br>Polynomial Register  | PRIMEPLUS_CRC_POLY    | Read/Write | 0x080F |

| 0xFEF7 - 0xFEF8 | CRC PRIMEPLUS Reset<br>Value Register | PRIMEPLUS_CRC_RST     | Read/Write | 0x0000 |

Table 7-1. Register Mapping

| Address         | Register                                 | Name       | Access     | Reset                  |

|-----------------|------------------------------------------|------------|------------|------------------------|

| 0xFEFA - 0xFEFD | Channel Selector Register                | CTPS       | Read/Write | 0x000150C7             |

| 0xFEFE          | Reserved                                 | -          | -          | 0x00                   |

| 0xFF00 - 0xFF07 | Reserved                                 | -          | -          | 0x411A1803<br>73D6893C |

| 0xFF09 - 0xFF0A | Reserved                                 | -          | -          | 0x0EA5                 |

| 0xFF0E - 0xFF11 | Peripheral CRC Polynomial Register       | VCRC_POLY  | Read/Write | 0x04C11DB7             |

| 0xFF12 - 0xFF15 | Peripheral CRC Reset Value<br>Register   | VCRC_RST   | Read/Write | 0x0000                 |

| 0xFF16          | Peripheral CRC<br>Configuration Register | VCRC_CONF  | Read/Write | 0xC3                   |

| 0xFF17          | Peripheral CRC Input<br>Register         | VCRC_INPUT | Read/Write | 0x00                   |

| 0xFF18          | Peripheral CRC Control<br>Register       | VCRC_CTL   | Read/Write | 0x00                   |

| 0xFF19 - 0xFF1C | Peripheral CRC Value<br>Register         | VCRC_CRC   | Read-only  | 0x0000                 |

| 0xFF1E          | Zero Crossing Configuration Register     | ZC_CONFIG  | Read/Write | 0x00                   |

| 0xFF1F - 0xFF20 | Reserved                                 | -          | -          | 0x051E                 |

| 0xFF21 - 0xFF22 | Reserved                                 | -          | -          | 0x8000                 |

| 0xFF23          | Zero Crossing Filter Register            | ZC_FILTER  | Read/Write | 0xB2                   |

| 0xFF24 - 0xFF27 | Reserved                                 | -          | -          | 0x00030D40             |

| 0xFF28 - 0xFF2B | Reserved                                 | -          | -          | 0x0000                 |

| 0xFF2D          | Reserved                                 | -          | -          | 0x01                   |

| 0xFF33 - 0xFF36 | Reserved                                 | -          | -          | 0x0000                 |

| 0xFF37 - 0xFF38 | Reserved                                 | -          | -          | 0x0000                 |

| 0xFF39          | Reserved                                 | -          | -          | 0x14                   |

| 0xFF3A          | Reserved                                 | -          | -          | 0x80                   |

| 0xFF3B          | Reserved                                 | -          | -          | 0x70                   |

| 0xFF3C          | Reserved                                 | -          | -          | 0xC8                   |

| 0xFF3D          | Reserved                                 | -          | -          | 0x0A                   |

| 0xFF3E          | Reserved                                 | -          | -          | 0x02                   |

| 0xFF3F          | Reserved                                 | -          | -          | 0x04                   |

| 0xFF40          | Reserved                                 | -          | -          | 0x01                   |

| 0xFF41          | Reserved                                 | -          | -          | 0x01                   |

| 0xFF42          | Reserved                                 | -          | -          | 0x27                   |

| 0xFF43          | Reserved                                 | -          | -          | 0x0A                   |

| 0xFF4C          | Reserved                                 | -          | -          | 0xA8                   |

| 0xFF51          | Reserved                                 | -          | -          | 0x99                   |

| 0xFF52          | Reserved                                 | -          | =          | 0xC0                   |

| 0xFF53          | Reserved                                 | -          | -          | 0x00                   |

| 0xFF54          | Reserved                                 | -          | -          | 0x03                   |

| 0xFF55          | Reserved                                 | -          | -          | 0x99                   |

| 0xFF56          | Reserved                                 | -          | _          | 0x99                   |

Table 7-1. Register Mapping

| Address         | Register | Name | Access | Reset  |

|-----------------|----------|------|--------|--------|

| 0xFF57          | Reserved | -    | -      | 0xFF   |

| 0xFF58          | Reserved | -    | -      | 0x33   |

| 0xFF5E - 0xFF5F | Reserved | -    | -      | 0x0000 |

| 0xFF61          | Reserved | -    | -      | 0x00   |

| 0xFF62          | Reserved | -    | -      | 0x10   |

| 0xFF63 - 0xFF64 | Reserved | -    | -      | 0x00BF |

| 0xFF65 - 0xFF66 | Reserved | -    | -      | 0x03E8 |

| 0xFF67 - 0xFF68 | Reserved | -    | -      | 0x0400 |

| 0xFF69 - 0xFF6A | Reserved | -    | -      | 0x0F20 |

| 0xFF6B - 0xFF6C | Reserved | -    | -      | 0x01EE |

| 0xFF6D - 0xFF6E |          | -    | -      | 0x00BF |

| 0xFF6F - 0xFF70 | Recorved | -    | -      | 0x0160 |

| 0xFF71 - 0xFF72 | Reserved | -    | -      | 0x02F0 |

| 0xFF73 - 0xFF74 |          | -    | -      | 0x0450 |

| 0xFF75          | Reserved | -    | -      | 0x68   |

| 0xFF76          | Reserved | -    | -      | 0x80   |

| 0xFF77          | Reserved | -    | -      | 0x3B   |

| 0xFF78 - 0xFF79 | Reserved | -    | -      | 0x0000 |

| 0xFF7A - 0xFF7F | Reserved | -    | -      | 0x0000 |

| 0xFF80          | Reserved | -    | -      | 0x00   |

| 0xFF81          | Reserved | -    | -      | 0x30   |

| 0xFF82 - 0xFF83 | Reserved | -    | -      | 0x0600 |

| 0xFF84          | Reserved | -    | -      | 0x58   |

| 0xFF85          | Reserved | -    | -      | 0x99   |

| 0xFF86          | Reserved | -    | -      | 0x79   |

| 0xFF87 - 0xFF88 | Reserved | -    | -      | 0x0021 |

| 0xFF89          | Reserved | -    | -      | 0x03   |

| 0xFF8A          | Reserved | -    | -      | 0x01   |

| 0xFF8B          | Reserved | -    | -      | 0x02   |

| 0xFF8C          | Reserved | -    | -      | 0x04   |

| 0xFF8D          | Reserved | -    | -      | 0x7F   |

| 0xFF8E          | Reserved | -    | -      | 0x00   |

| 0xFF92          | Reserved | -    | -      | 0x14   |

| 0xFF93          | Reserved | -    | -      | 0x11   |

| 0xFF94          | Reserved | -    | -      | 0x80   |

| 0xFF95          | Reserved | -    | -      | 0x00   |

| 0xFF96          | Reserved | -    | -      | 0x00   |

| 0xFF97          | Reserved | -    | -      | 0x70   |

| 0xFF98          | Reserved | -    | -      | 0xC8   |

| 0xFF99          | Reserved | -    | -      | 0x0A   |

| 0xFF9A          | Reserved | -    | _      | 0x02   |

| 0xFF9B          | Reserved | -    | _      | 0x04   |

Table 7-1. Register Mapping

| Address         | Register                              | Name     | Access     | Reset  |

|-----------------|---------------------------------------|----------|------------|--------|

| 0xFF9C          | Reserved                              | -        | -          | 0x01   |

| 0xFF9D          | Reserved                              | -        | -          | 0x01   |

| 0xFF9E          | Reserved                              | -        | -          | 0x27   |

| 0xFF9F          | Reserved                              | -        | -          | 0x0A   |

| 0xFFA0 - 0xFFAF | Peripheral AES Key Register           | AES_KEY  | Read/Write | 0x0000 |

| 0xFFB0 - 0xFFBF | Peripheral AES Data Field<br>Register | AES_DATA | Read/Write | 0x0000 |

| 0xFFC0          | Peripheral AES Control<br>Register    | AES_CTL  | Read/Write | 0x04   |

| 0xFFE2 - 0xFFE3 |                                       | -        | -          | 0x0424 |

| 0xFFE4 - 0xFFE5 |                                       | -        | -          | 0x0424 |

| 0xFFE6 - 0xFFE7 |                                       | -        | -          | 0x0424 |

| 0xFFE8 - 0xFFE9 |                                       | -        | -          | 0x0424 |

| 0xFFEA - 0xFFEB |                                       | -        | -          | 0x0424 |

| 0xFFEC - 0xFFED | Reserved                              | -        | -          | 0x0424 |

| 0xFFEE - 0xFFEF | - Vesci Aga                           | -        | -          | 0x0424 |

| 0xFFF0 - 0xFFF1 |                                       | -        | -          | 0x0424 |

| 0xFFF2 - 0xFFF3 |                                       | -        | -          | 0x0424 |

| 0xFFF4 - 0xFFF5 |                                       | -        | -          | 0x0424 |

| 0xFFF6 - 0xFFF7 |                                       | -        | -          | 0x0424 |

| 0xFFF8 - 0xFFF9 |                                       | -        | -          | 0x0424 |

## 8. MAC Coprocessor

ATPL230A accelerators can be used to perform PRIME MAC-specific tasks by hardware, decreasing CPU load from the external MCU/MPU. For that purpose, Cyclic Redundance Check (CRC) and AES128 encryption blocks are available in ATPL230A.

Please refer to Atmel doc43048 "Atmel PRIME Implementation" for Atmel software package detailed description and functionality.

### 8.1 Cyclic Redundancy Check (CRC)

#### 8.1.1 PRIME v1.3 CRC

There are three types of MAC PDUs (generic, promotion and beacon) for different purposes, and each one has its own specific CRC. There is a hardware implementation of every CRC type calculated by the MAC layer. This CRC hardware-calculation is enabled by default. Note that the CRC included at the physical layer is also a hardware implementation available (enabled by default).

Generic MAC Header

Packet 1

Packet n

CRC

MSB

Unused HDR.HT Reserved

Reserved HDR.DO HDR. LEVEL

HDR. HCS

Figure 8-1. Example: Generic MAC PDU format and generic MAC header detail

In transmission all CRC bytes are real-time calculated and the last bytes of the MAC PDU are overwritten with these values, (provided that the field HT in the first byte of the MAC header in transmission data is equal to the corresponding MAC PDU type).

LSB

In reception the CRC bytes are also real-time calculated and these bytes are checked with the last bytes of the MAC PDU. If the CRC is not correct, then an error flag is activated, the complete frame is discarded, and the corresponding error counter is increased. These counters allow the MAC layer to take decisions according to error ratio.

**For the Generic MAC PDU**, there is an 8-bit CRC in the Generic MAC header, which corresponds to PRIME HDR.HCS. In reception, if this CRC doesn't check successfully, the current frame is discarded and no interruption is generated.

This works in the same way as CRC for the PHY layer (CRC Ctrl, located in the PHY header, see PRIME specification for further information).

There is another CRC for the Generic MAC PDU which is the last field of the GPDU. It is 32 bits long and it is used to detect transmission errors. The CRC shall cover the concatenation of the SNA with the GPDU except for the CRC field itself. In reception, if the CRC is not successful then an internal flag is set and the error counter is increased.

**For the Promotion Needed PDU** there is an 8-bit CRC, calculated with the first 13 bytes of the header. In reception, if this CRC is not correct, then an internal flag is set and the corresponding error counter is increased.

For the Beacon PDU there is a 32-bit CRC calculated with the same algorithm as the one defined for the CRC of the Generic MAC PDU. This CRC shall be calculated over the complete BPDU except for the CRC field itself. In reception, if this CRC is not successful, then an internal flag is set and the same error counter used for GPDU is increased. The hardware used for this CRC is the same as the one used for GPDU.

#### 8.1.2 Configurable CRC calculation

PRIME v1.3 version fixes the polynomial to calculate the CRCs. In case that these polynomials were modified, the CRC peripheral would be used. It is used as a peripheral unit, accessible using the system peripheral registers.

For example, to configure it for PRIME CRC8:

```

X^8 + X^2 + X + 1

VCRC_POLY = 0x00000007

VCRC_RST = 0x00000000

VCRC_CONF = 0xC0

```

And to configure it for PRIME CRC32:

```

x^32 + x^26 + x^23 + x^22 + x^16 + x^12 + x^11 + x^10 + x^8 + x^7 + x^5 + x^4 + x^2 + x + 1

VCRC_POLY = 0x04C11DB7

VCRC_RST = 0x00000000

VCRC_CONF = 0xC3

```

A different set of registers can also be used to set CRC parameters:

```

X^12 + X^11 + X^3 + X^2 + X + 1

PRIMEPLUS_CRC_POLY = 0x080F

PRIMEPLUS_CRC_RST = 0x0000

PRIMEPLUS_CRC_CONFIG = 0x14

```

### 8.2 Advanced Encryption Standard (AES)

One of the additional security functionalities to PRIME v1.3 is the 128-bit AES encryption of data. ATPL230A includes a hardware implementation of this block, as a peripheral unit.

In transmission, data must be encrypted previously to the use of the PHY\_DATA request primitive (see PRIME specification), in an independent way (note that Beacon PDU, Promotion PDU and Generic MAC header, as well as several control packets, are not encrypted).

In reception, data passed by the PHY layer is already encrypted and must be decrypted in a subsequent process.

To encrypt a data package with corresponding KEY, the process is as follows:

- 1. Write the KEY (128 bits long) in AES\_KEY register. This step is only needed if a new key is going to be used (due to a key change or to a reset operation).

- 2. Write the 128 bits of data to be encrypted in AES DATA register.

- 3. Set to '1' the CIPHER control bit in AES\_CTL register and then set to '1' the START control bit to start the operation. This step could be realized as an atomic operation writing 0x03.

- 4. Wait until the READY bit in AES\_CTL register becomes '1' automatically. This bit indicates when the operation is completed.

- 5. After that, the encrypted (coded) data package is automatically stored in AES\_DATA register.

On the other hand, to decrypt a data package with corresponding KEY, the process is as follows:

- 1. Write the KEY (128 bits long) in AES\_KEY register. This step is only needed if a new key is going to be used (due to a key change or to a reset operation).

- 2. Write the 128 bits of encrypted data in AES DATA register.

- 3. Set to '0' the CIPHER control bit in AES\_CTL register and then set to '1' the START control bit to start the operation. This step could be realized as an atomic operation writing 0x02.

- 4. Wait until the READY bit in AES\_CTL register becomes '1' automatically. This bit indicates when the operation is completed.

- 5. After that, the decrypted (decoded) data package is automatically stored in AES\_DATA register.

# 8.3 MAC Coprocessor Registers

### 8.3.1 CRC Registers

### 8.3.1.1 Sub Network Address Register

Name: SNA

Address: 0xFE62 – 0xFE67

Access: Read/Write Reset: 0x00..00

| 47          | 46          | 45 | 44    | 43      | 42 | 41 | 40 |  |  |  |  |  |

|-------------|-------------|----|-------|---------|----|----|----|--|--|--|--|--|

| SNA (47:40) |             |    |       |         |    |    |    |  |  |  |  |  |

| 39          | 38          | 37 | 36    | 35      | 34 | 33 | 32 |  |  |  |  |  |

|             | SNA (39:32) |    |       |         |    |    |    |  |  |  |  |  |

| 31          | 30          | 29 | 28    | 27      | 26 | 25 | 24 |  |  |  |  |  |

|             |             |    | SNA ( | (31:24) |    |    |    |  |  |  |  |  |

| 23          | 22          | 21 | 20    | 19      | 18 | 17 | 16 |  |  |  |  |  |

|             |             |    | SNA ( | (23:16) |    |    |    |  |  |  |  |  |

| 15          | 14          | 13 | 12    | 11      | 10 | 9  | 8  |  |  |  |  |  |

|             |             |    | SNA   | (15:8)  |    |    |    |  |  |  |  |  |

| 7           | 6           | 5  | 4     | 3       | 2  | 1  | 0  |  |  |  |  |  |

|             |             |    | SNA   | (7:0)   |    |    |    |  |  |  |  |  |

This register stores the 48-bit Sub Network Address. Physical layer uses it to calculate the CRC's.

### 8.3.1.2 CRC32 Errors Counter Register

Name: ERR\_CRC32\_MAC

Address: 0xFEBA (MSB) - 0xFEBB (LSB)

Access: Read-only Reset: 0x0000

| 15                   | 14                  | 13 | 12 | 11 | 10 | 9 | 8 |  |  |  |

|----------------------|---------------------|----|----|----|----|---|---|--|--|--|

| ERR_CRC32_MAC (15:8) |                     |    |    |    |    |   |   |  |  |  |

| 7                    | 6                   | 5  | 4  | 3  | 2  | 1 | 0 |  |  |  |

|                      | ERR_CRC32_MAC (7:0) |    |    |    |    |   |   |  |  |  |

This register stores the number of received PRIME v1.3 packets (Beacon and generic) with an error in the CRC32 MAC field of the payload, since the last physical layer reset. Only a physical layer reset initializes the register.

### 8.3.1.3 CRC8 Errors Counter Register

Name: ERR\_CRC8\_MAC

Address: 0xFEBC (MSB) – 0xFEBD (LSB)

Access: Read-only Reset: 0x0000

| 15                  | 14                 | 13 | 12 | 11 | 10 | 9 | 8 |  |  |  |

|---------------------|--------------------|----|----|----|----|---|---|--|--|--|

| ERR_CRC8_MAC (15:8) |                    |    |    |    |    |   |   |  |  |  |

| 7                   | 6                  | 5  | 4  | 3  | 2  | 1 | 0 |  |  |  |

|                     | ERR_CRC8_MAC (7:0) |    |    |    |    |   |   |  |  |  |

This register stores the number of received PRIME v1.3 packets (Promotion) with an error in the CRC8 MAC field of the payload, since the last physical layer reset. Only a physical layer reset initializes the register.

### 8.3.1.4 CRC8 HD Errors Counter Register

Name: ERR\_CRC8\_MAC\_HD

Address: 0xFEC0 (MSB) – 0xFEC1 (LSB)

Access: Read-only Reset: 0x0000

| 15                     | 14                    | 13 | 12 | 11 | 10 | 9 | 8 |  |  |  |

|------------------------|-----------------------|----|----|----|----|---|---|--|--|--|

| ERR_CRC8_MAC_HD (15:8) |                       |    |    |    |    |   |   |  |  |  |

| 7                      | 6                     | 5  | 4  | 3  | 2  | 1 | 0 |  |  |  |

|                        | ERR_CRC8_MAC_HD (7:0) |    |    |    |    |   |   |  |  |  |

This register stores the number of received PRIME v1.3 packets with an error in the CRC8 MAC field of the header, since the last physical layer reset. Only a physical layer reset initializes the register.

### 8.3.1.5 CRC8 PHY Errors Counter Register

Name: ERR\_CRC8\_PHY

Address: 0xFEC2 (MSB) – 0xFEC3 (LSB)

Access: Read-only Reset: 0x0000

| 15                  | 14                 | 13 | 12 | 11 | 10 | 9 | 8 |  |  |  |

|---------------------|--------------------|----|----|----|----|---|---|--|--|--|

| ERR_CRC8_PHY (15:8) |                    |    |    |    |    |   |   |  |  |  |

| 7                   | 6                  | 5  | 4  | 3  | 2  | 1 | 0 |  |  |  |

|                     | ERR_CRC8_PHY (7:0) |    |    |    |    |   |   |  |  |  |

This register stores the number of received PRIME v1.3 packets with an error in the CRC8 PHY field of the header, since the last physical layer reset. Only a physical layer reset initializes the register.

### 8.3.1.6 CRC PRIMEPLUS Configuration Register

Name: PRIMEPLUS\_CRC\_CONFIG

Address: 0xFEF4

Access: Read/Write

Reset: 0x14

| 7 | 6 | 5 | 4       | 3     | 2 | 1 | 0 |

|---|---|---|---------|-------|---|---|---|

| - | - | - | FB_TYPE | WIDTH |   |   |   |

PRIMEPLUS\_CRC\_CONFIG register allows the user to configure feedback type and width of the PRIME v1.4 mode physical CRC computation algorithm.

#### FB\_TYPE:

'0': Computation procedure must end with extra bytes with value zero added to the data ones (User added).

'1': Extra bytes addition is not required.

### • WIDTH (3:0):

Represents the grade of the polynomial used by the algorithm.

| WIDTH (3:0) | Polynomial bits |

|-------------|-----------------|

| 0           | 8               |

| 1           | 9               |

| 2           | 10              |

| 3           | 11              |

| 4           | 12              |

| 5           | 13              |

| 6           | 14              |

| 7           | 15              |

| >7          | 16              |

### 8.3.1.7 CRC PRIMEPLUS Polynomial Register

Name: PRIMEPLUS CRC POLY

Address: 0xFEF5 (MSB) - 0xFEF6 (LSB)

Access: Read/Write

Reset: 0x080F

| 15                        | 14                       | 13 | 12 | 11 | 10 | 9 | 8 |  |  |  |

|---------------------------|--------------------------|----|----|----|----|---|---|--|--|--|

| PRIMEPLUS_CRC_POLY (15:8) |                          |    |    |    |    |   |   |  |  |  |

| 7                         | 6                        | 5  | 4  | 3  | 2  | 1 | 0 |  |  |  |

|                           | PRIMEPLUS_CRC_POLY (7:0) |    |    |    |    |   |   |  |  |  |