# NCT6686D Nuvoton eSIO

# HARDWARE DATASHEET (External Architecture)

Date: April 21, 2017 Revision 0.5

# **TABLE OF CONTENTS -**

| 1. | GE   | NERAL DESCRIPTION                        | 2    |

|----|------|------------------------------------------|------|

| 2. | FE.  | ATURES                                   | 3    |

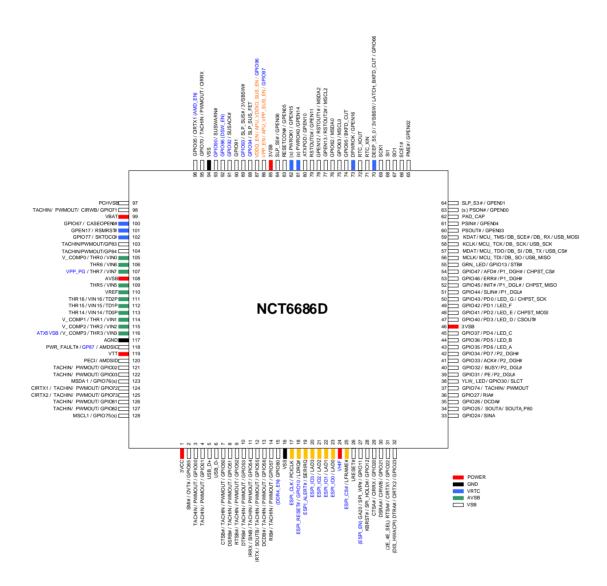

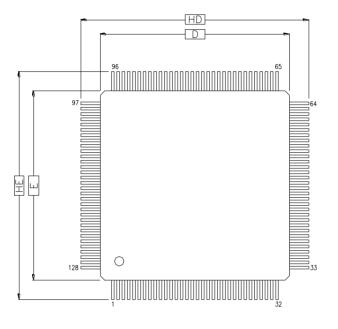

| 3. | PIN  | N LAYOUT                                 | 8    |

|    | 3.1  | PIN MULTIPLEXING                         |      |

| 4. | PIN  | N DESCRIPTION                            |      |

|    | 4.1  | LPC Interface                            |      |

|    | 4.2  | ESPI Interface                           |      |

|    | 4.3  | Multi-Mode Parallel Port                 |      |

|    | 4.4  | Serial Port Interface                    |      |

|    | 4.5  | KBC Interface                            |      |

|    | 4.6  | CIR Interface                            |      |

|    | 4.7  | Hardware Monitor Interface               |      |

|    | 4.8  | SPI Interface                            |      |

|    | 4.9  | PECI Interface                           |      |

|    | 4.10 | SB-TSI Interface                         |      |

|    | 4.11 | Advanced Configuration & Power Interface |      |

|    | 4.12 | Port 80 Message Display & LED Control    |      |

|    | 4.13 | SMBus Interface                          |      |

|    | 4.14 | USB                                      |      |

|    | 4.15 | PORT80 to UART                           |      |

|    | 4.16 | IR                                       |      |

|    | 4.17 | SPI Switch Controller                    |      |

|    | 4.18 | Advanced Sleep State Control             |      |

|    | 4.19 | RTC Crystal Oscillator                   |      |

|    | 4.20 | DDR4 Power Sequence                      |      |

|    | 4.21 | AMD DDR4 Power Sequence                  |      |

|    | 4.22 | Strapping Pins                           |      |

|    | 4.23 | Power Pins                               |      |

|    | 4.24 | General Purpose I/O Port                 |      |

|    | 4.24 | •                                        |      |

|    | 4.2  |                                          |      |

|    | 4.2  |                                          |      |

|    | 4.2  | 4.4 GPIO-3 Interface                     |      |

|    | 4.2  | 4.5 GPIO-4 Interface                     | 27   |

|    | 4.2  | 4.6 GPIO-5 Interface                     | 28   |

|    | 4.2  | 4.7 GPIO-6 Interface                     | 29   |

|    | 4.2  | 4.8 GPIO-7 Interface                     | 29   |

|    | 4.2  | 4.9 GPIO-8 Interface                     | 30   |

|    | 4.2  | 4.1 GPIO-9 Interface                     | 31   |

|    | 4.2  | 4.2 GPIO EN0 Interface                   | 31   |

|    | 4.2  | 4.3 GPIO EN1 Interface                   | 32   |

|    | 4.25 | Debug PORT Test                          | . 33 |

|    | 4.26 | DSW                                      | . 33 |

|    | 4.27 | Power Fault                              | . 33 |

|              | 4.28 In                                                                                                                                                                                             | ternal pull-up, pull-down pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                      |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| 5.           | GLUE                                                                                                                                                                                                | LOGIC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 34                                   |

| į            | 5.1 A                                                                                                                                                                                               | CPI Glue Logic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 34                                   |

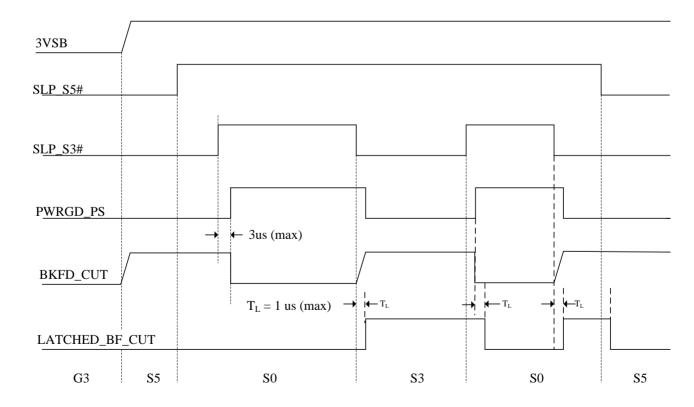

| į            | 5.2 BI                                                                                                                                                                                              | KFD_CUT and LATCHED_BF_CUT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 36                                   |

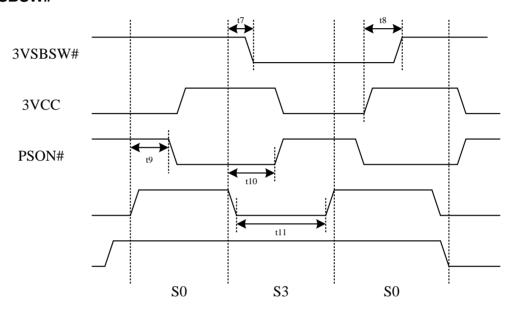

| į            |                                                                                                                                                                                                     | /SBSW#                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                      |

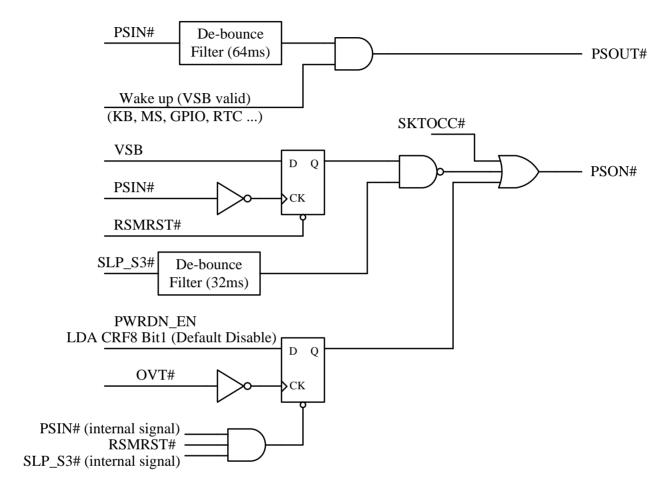

| į            |                                                                                                                                                                                                     | SON# Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                      |

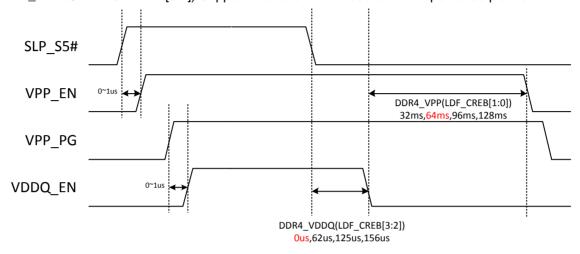

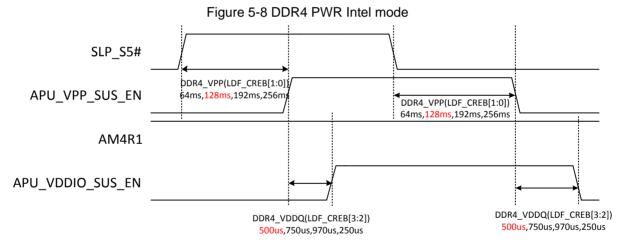

|              |                                                                                                                                                                                                     | DR4PWR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                      |

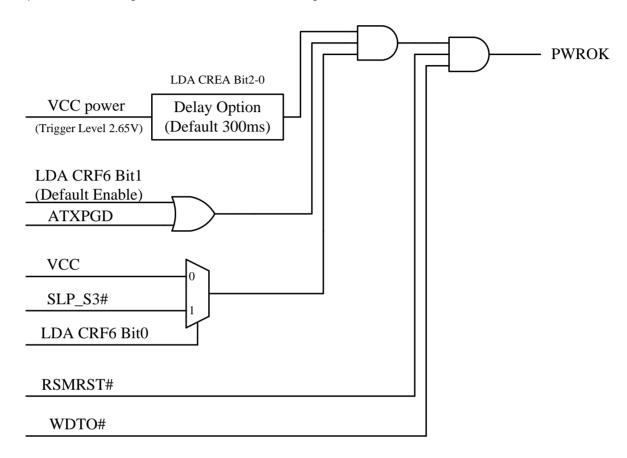

|              |                                                                                                                                                                                                     | WROK Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                      |

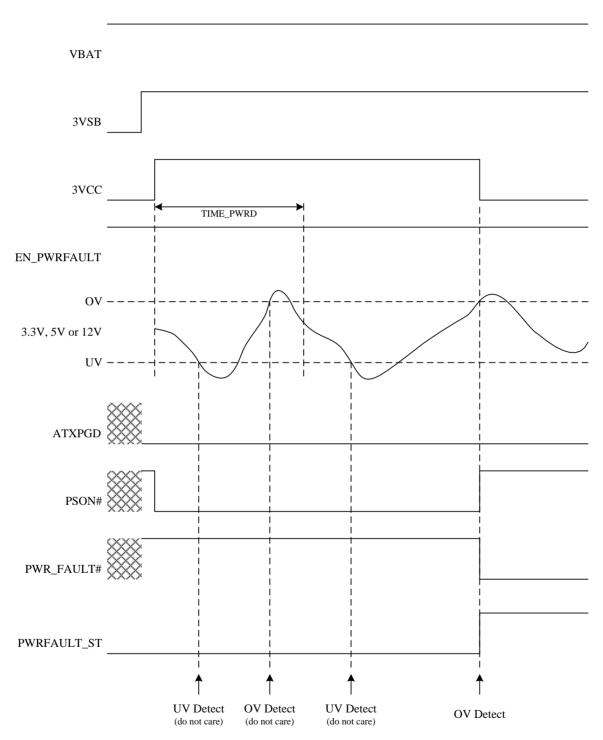

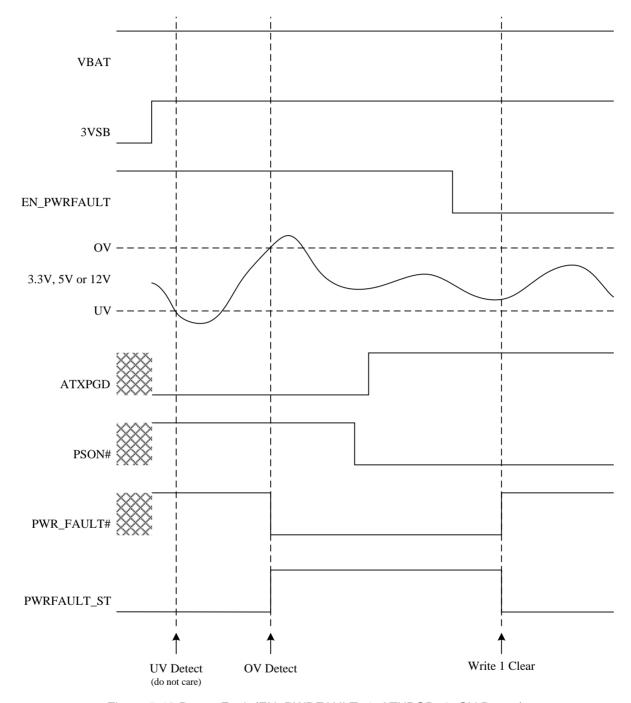

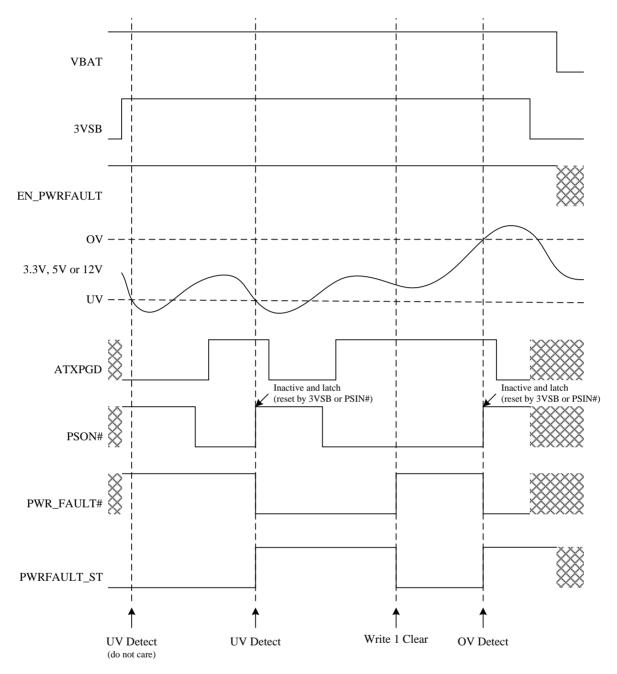

|              |                                                                                                                                                                                                     | ower Fault                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                      |

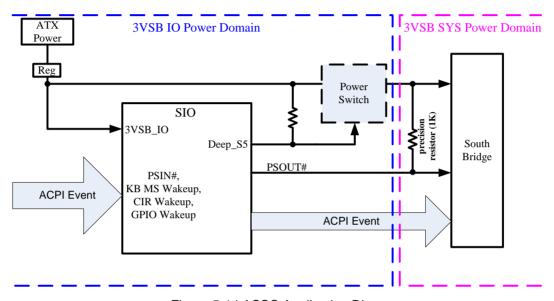

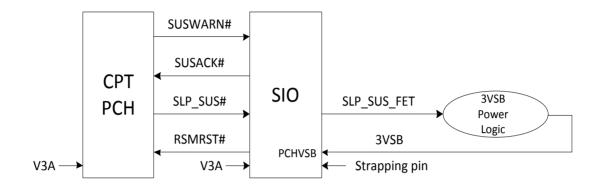

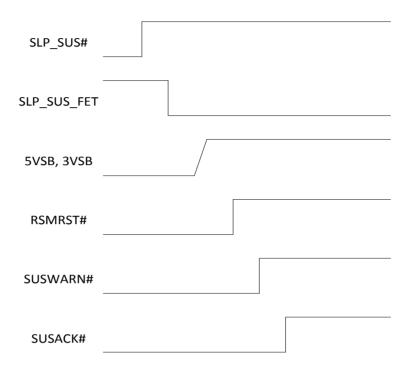

|              |                                                                                                                                                                                                     | dvanced Sleep State Control (ASSC) Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                      |

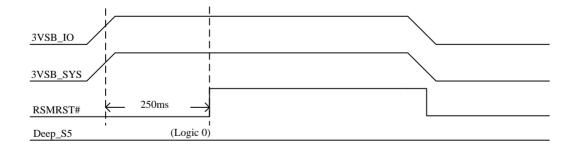

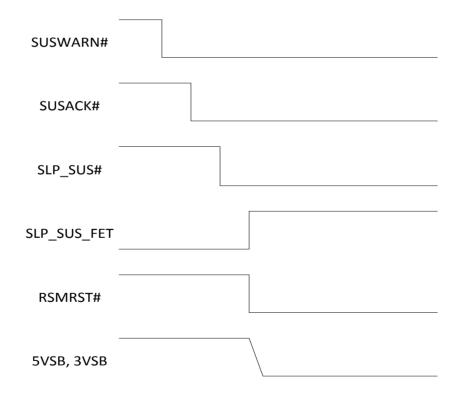

|              | 5.8.1                                                                                                                                                                                               | When ASSC is disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                      |

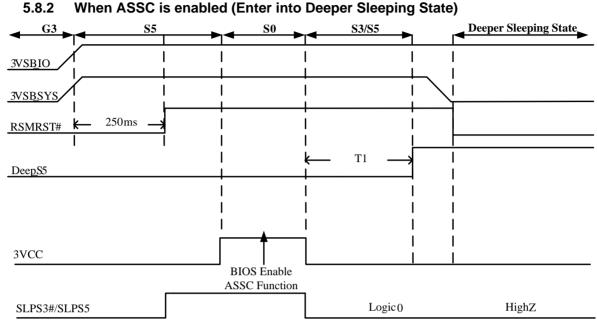

|              | 5.8.2                                                                                                                                                                                               | When ASSC is enabled (Enter into Deeper Sleeping State)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                      |

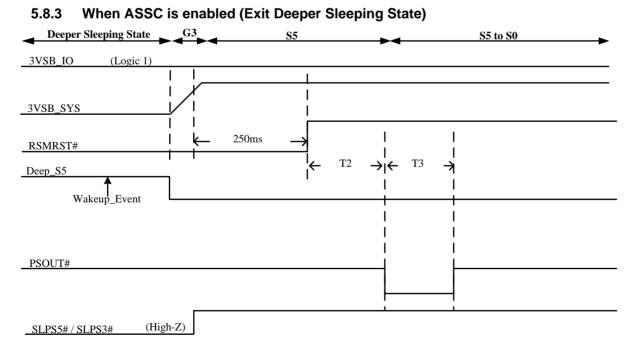

|              | 5.8.3                                                                                                                                                                                               | When ASSC is enabled (Exit Deeper Sleeping State)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                      |

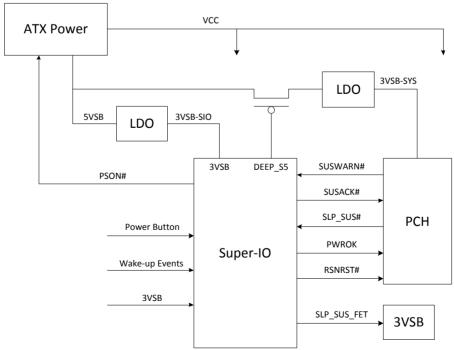

| į            | 5.9 In                                                                                                                                                                                              | tel DSW Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 46                                   |

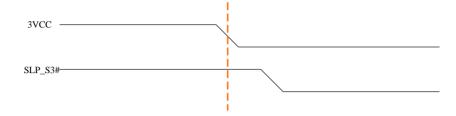

|              | 5.9.1                                                                                                                                                                                               | Enter DSW State timing diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                      |

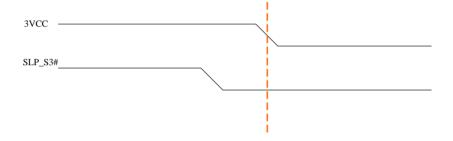

|              | 5.9.2                                                                                                                                                                                               | Exit DSW State timing diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 47                                   |

|              | 5.9.3                                                                                                                                                                                               | Application Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 47                                   |

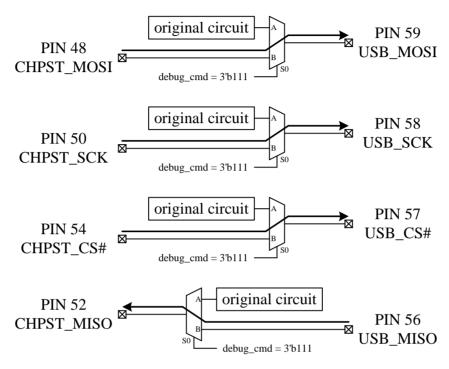

| į            | 5.10 SI                                                                                                                                                                                             | PI Switch Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 48                                   |

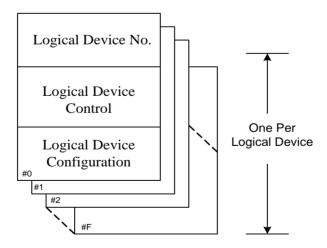

| 6.           | CONF                                                                                                                                                                                                | FIGURATION REGISTER ACCESS PROTOCOL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 50                                   |

| (            | 6.1 C                                                                                                                                                                                               | onfiguration Sequence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 52                                   |

|              | 6.1.1                                                                                                                                                                                               | Enter the Extended Function Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                      |

|              |                                                                                                                                                                                                     | Configure the Configuration Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 52                                   |

|              | 6.1.2                                                                                                                                                                                               | Configure the Configuration Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                      |

|              | 6.1.2<br>6.1.3                                                                                                                                                                                      | Exit the Extended Function Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 53                                   |

|              |                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                      |

| 7.           | 6.1.3<br>6.1.4                                                                                                                                                                                      | Exit the Extended Function Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 53                                   |

|              | 6.1.3<br>6.1.4<br>EC SI                                                                                                                                                                             | Exit the Extended Function Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 53<br>56                             |

| -            | 6.1.3<br>6.1.4<br>EC SI<br>7.1 Fe                                                                                                                                                                   | Exit the Extended Function Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 53<br>56                             |

| -            | 6.1.3<br>6.1.4<br>EC SI<br>7.1 Fe                                                                                                                                                                   | Exit the Extended Function Mode  Software Programming Example  PACE  eatures Implemented by Firmware                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 53<br>56<br>56                       |

| -            | 6.1.3<br>6.1.4<br>EC SI<br>7.1 Fe<br>7.2 E0                                                                                                                                                         | Exit the Extended Function Mode Software Programming Example PACE eatures Implemented by Firmware C Space Register Set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 53<br>56<br>56                       |

| -            | 6.1.3<br>6.1.4<br>EC SI<br>7.1 Fe<br>7.2 E0<br>7.2.1                                                                                                                                                | Exit the Extended Function Mode  Software Programming Example  PACE  eatures Implemented by Firmware  C Space Register Set  Page Port0 – Base Address0 + 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 53<br>56<br>56<br>56                 |

| -            | 6.1.3<br>6.1.4<br>EC SI<br>7.1 Fe<br>7.2 E0<br>7.2.1<br>7.2.2                                                                                                                                       | Exit the Extended Function Mode Software Programming Example.  PACE Seatures Implemented by Firmware C Space Register Set Page Port0 – Base Address0 + 0 Index Port0 – Base Address0 + 1 Data Port0 – Base Address0 + 2 Host Interface Event Register0 – Base Address0 + 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 53<br>56<br>56<br>57                 |

| -            | 6.1.3<br>6.1.4<br>EC SI<br>7.1 Fe<br>7.2 E0<br>7.2.1<br>7.2.2<br>7.2.3                                                                                                                              | Exit the Extended Function Mode Software Programming Example PACE eatures Implemented by Firmware C Space Register Set Page Port0 – Base Address0 + 0 Index Port0 – Base Address0 + 1 Data Port0 – Base Address0 + 2 Host Interface Event Register0 – Base Address0 + 3 Page Port1 – Base Address0 + 4                                                                                                                                                                                                                                                                                                                                                                                                                                      | 535656565757                         |

| -            | 6.1.3<br>6.1.4<br>EC SI<br>7.1 Fe<br>7.2 E0<br>7.2.1<br>7.2.2<br>7.2.3<br>7.2.4                                                                                                                     | Exit the Extended Function Mode Software Programming Example PACE Patures Implemented by Firmware C Space Register Set Page Port0 – Base Address0 + 0 Index Port0 – Base Address0 + 1 Data Port0 – Base Address0 + 2 Host Interface Event Register0 – Base Address0 + 3 Page Port1 – Base Address0 + 4 Index Port1 – Base Address0 + 5                                                                                                                                                                                                                                                                                                                                                                                                      | 535656575757                         |

| -            | 6.1.3<br>6.1.4<br>EC SI<br>7.1 Fe<br>7.2 E0<br>7.2.1<br>7.2.2<br>7.2.3<br>7.2.4<br>7.2.5<br>7.2.6<br>7.2.7                                                                                          | Exit the Extended Function Mode Software Programming Example PACE Patures Implemented by Firmware C Space Register Set Page Port0 – Base Address0 + 0 Index Port0 – Base Address0 + 1 Data Port0 – Base Address0 + 2 Host Interface Event Register0 – Base Address0 + 3 Page Port1 – Base Address0 + 4 Index Port1 – Base Address0 + 5 Data Port1 – Base Address0 + 6                                                                                                                                                                                                                                                                                                                                                                       | 5356565757575757                     |

| -            | 6.1.3<br>6.1.4<br>EC SI<br>7.1 Fe<br>7.2 E0<br>7.2.1<br>7.2.2<br>7.2.3<br>7.2.4<br>7.2.5<br>7.2.6<br>7.2.7<br>7.2.8                                                                                 | Exit the Extended Function Mode Software Programming Example PACE Patures Implemented by Firmware C Space Register Set Page Port0 – Base Address0 + 0 Index Port0 – Base Address0 + 1 Data Port0 – Base Address0 + 2 Host Interface Event Register0 – Base Address0 + 3 Page Port1 – Base Address0 + 4 Index Port1 – Base Address0 + 5 Data Port1 – Base Address0 + 6 Host Interface Event Register1 – Base Address0 + 7                                                                                                                                                                                                                                                                                                                    | 535656575757575757                   |

| 7            | 6.1.3<br>6.1.4<br>EC SI<br>7.1 Fe<br>7.2 E0<br>7.2.1<br>7.2.2<br>7.2.3<br>7.2.4<br>7.2.5<br>7.2.6<br>7.2.7<br>7.2.8                                                                                 | Exit the Extended Function Mode Software Programming Example PACE Patures Implemented by Firmware C Space Register Set Page Port0 – Base Address0 + 0 Index Port0 – Base Address0 + 1 Data Port0 – Base Address0 + 2 Host Interface Event Register0 – Base Address0 + 3 Page Port1 – Base Address0 + 4 Index Port1 – Base Address0 + 5 Data Port1 – Base Address0 + 6                                                                                                                                                                                                                                                                                                                                                                       | 535656575757575757                   |

| 7            | 6.1.3<br>6.1.4<br>EC SI<br>7.1 Fe<br>7.2 E0<br>7.2.1<br>7.2.2<br>7.2.3<br>7.2.4<br>7.2.5<br>7.2.6<br>7.2.7<br>7.2.8<br>7.3 O                                                                        | Exit the Extended Function Mode Software Programming Example PACE Patures Implemented by Firmware C Space Register Set Page Port0 – Base Address0 + 0 Index Port0 – Base Address0 + 1 Data Port0 – Base Address0 + 2 Host Interface Event Register0 – Base Address0 + 3 Page Port1 – Base Address0 + 4 Index Port1 – Base Address0 + 5 Data Port1 – Base Address0 + 6 Host Interface Event Register1 – Base Address0 + 7                                                                                                                                                                                                                                                                                                                    | 535656575757575757575858             |

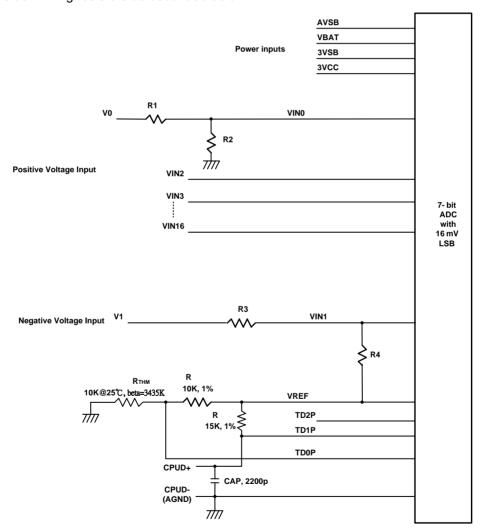

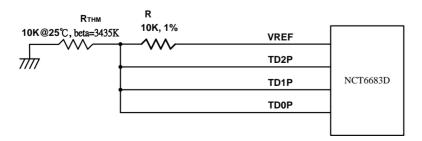

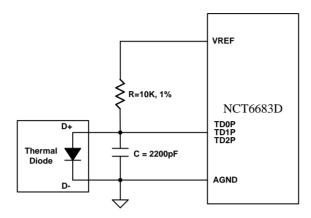

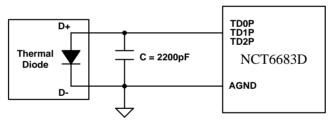

| 8.           | 6.1.3<br>6.1.4<br>EC SI<br>7.1 Fe<br>7.2 E0<br>7.2.1<br>7.2.2<br>7.2.3<br>7.2.4<br>7.2.5<br>7.2.6<br>7.2.7<br>7.2.8<br>7.3 O<br>ANAL                                                                | Exit the Extended Function Mode Software Programming Example PACE Pactures Implemented by Firmware C Space Register Set Page Port0 – Base Address0 + 0 Index Port0 – Base Address0 + 1 Data Port0 – Base Address0 + 2 Host Interface Event Register0 – Base Address0 + 3 Page Port1 – Base Address0 + 4 Index Port1 – Base Address0 + 5 Data Port1 – Base Address0 + 6 Host Interface Event Register1 – Base Address0 + 7 perations on EC Space OG INPUTS Ditages Over 2.048 V or Less Than 0 V                                                                                                                                                                                                                                             | 5356565757575758585858               |

| 8.           | 6.1.3<br>6.1.4<br>EC SI<br>7.1 Fe<br>7.2 E0<br>7.2.1<br>7.2.2<br>7.2.3<br>7.2.4<br>7.2.5<br>7.2.6<br>7.2.7<br>7.2.8<br>7.3 O<br>ANAL                                                                | Exit the Extended Function Mode Software Programming Example.  PACE  Patures Implemented by Firmware  C Space Register Set  Page Port0 – Base Address0 + 0  Index Port0 – Base Address0 + 1  Data Port0 – Base Address0 + 2  Host Interface Event Register0 – Base Address0 + 3  Page Port1 – Base Address0 + 4  Index Port1 – Base Address0 + 5  Data Port1 – Base Address0 + 6  Host Interface Event Register1 – Base Address0 + 7  perations on EC Space  OG INPUTS                                                                                                                                                                                                                                                                      | 5356565757575758585858               |

| 8.           | 6.1.3<br>6.1.4<br>EC SI<br>7.1 Fe<br>7.2 E0<br>7.2.1<br>7.2.2<br>7.2.3<br>7.2.4<br>7.2.5<br>7.2.6<br>7.2.7<br>7.2.8<br>7.3 O<br>ANAL<br>8.1 Vo                                                      | Exit the Extended Function Mode Software Programming Example PACE Pactures Implemented by Firmware C Space Register Set Page Port0 – Base Address0 + 0 Index Port0 – Base Address0 + 1 Data Port0 – Base Address0 + 2 Host Interface Event Register0 – Base Address0 + 3 Page Port1 – Base Address0 + 4 Index Port1 – Base Address0 + 5 Data Port1 – Base Address0 + 6 Host Interface Event Register1 – Base Address0 + 7 perations on EC Space OG INPUTS Ditages Over 2.048 V or Less Than 0 V                                                                                                                                                                                                                                             | 53565656575757585858585858           |

| 8.<br>{<br>{ | 6.1.3<br>6.1.4<br>EC SI<br>7.1 Fe<br>7.2 E0<br>7.2.1<br>7.2.2<br>7.2.3<br>7.2.4<br>7.2.5<br>7.2.6<br>7.2.7<br>7.2.8<br>7.3 O<br>ANAL<br>8.1 Vo<br>8.2 M                                             | Exit the Extended Function Mode Software Programming Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5356565657575758585858585858         |

| 8.<br>{<br>{ | 6.1.3<br>6.1.4<br>EC SI<br>7.1 Fe<br>7.2 E0<br>7.2.1<br>7.2.2<br>7.2.3<br>7.2.4<br>7.2.5<br>7.2.6<br>7.2.7<br>7.2.8<br>7.3 O<br>ANAL<br>8.1 Vo<br>8.2 M<br>8.3 M<br>8.4 M                           | Exit the Extended Function Mode Software Programming Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 53565656575757575858585858585858     |

| 8.           | 6.1.3<br>6.1.4<br>EC SI<br>7.1 Fe<br>7.2 E0<br>7.2.1<br>7.2.2<br>7.2.3<br>7.2.4<br>7.2.5<br>7.2.6<br>7.2.7<br>7.2.8<br>7.3 O<br>ANAL<br>8.1 Vo<br>8.2 M<br>8.3 M<br>8.4 M                           | Exit the Extended Function Mode Software Programming Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5356565657575758585858585858         |

| 8.           | 6.1.3<br>6.1.4<br>EC SI<br>7.1 Fe<br>7.2 E0<br>7.2.1<br>7.2.2<br>7.2.3<br>7.2.4<br>7.2.5<br>7.2.6<br>7.2.7<br>7.2.8<br>7.3 O<br>ANAL<br>8.1 Vo<br>8.2 M<br>8.3 M<br>8.4 M<br>UART                   | Exit the Extended Function Mode Software Programming Example PACE Batures Implemented by Firmware C Space Register Set Page Port0 – Base Address0 + 0 Index Port0 – Base Address0 + 1 Data Port0 – Base Address0 + 2 Host Interface Event Register0 – Base Address0 + 3 Page Port1 – Base Address0 + 4 Index Port1 – Base Address0 + 5 Data Port1 – Base Address0 + 6 Host Interface Event Register1 – Base Address0 + 7 perations on EC Space OG INPUTS Ditages Over 2.048 V or Less Than 0 V onitor Temperature from Thermistor onitor Temperature from Thermal Diode (Voltage Mode) onitor Temperature from Thermal Diode (Current Mode)                                                                                                 | 53565656575757585858585858585858     |

| 8.           | 6.1.3<br>6.1.4<br>EC SI<br>7.1 Fe<br>7.2 E0<br>7.2.1<br>7.2.2<br>7.2.3<br>7.2.4<br>7.2.5<br>7.2.6<br>7.2.7<br>7.2.8<br>7.3 O<br>ANAL<br>8.1 Vo<br>8.2 M<br>8.3 M<br>8.4 M<br>UART<br>9.1.1          | Exit the Extended Function Mode Software Programming Example.  PACE Batures Implemented by Firmware C Space Register Set. Page Port0 – Base Address0 + 0. Index Port0 – Base Address0 + 1. Data Port0 – Base Address0 + 2. Host Interface Event Register0 – Base Address0 + 3 Page Port1 – Base Address0 + 4. Index Port1 – Base Address0 + 5. Data Port1 – Base Address0 + 6. Host Interface Event Register1 – Base Address0 + 7 perations on EC Space. OG INPUTS Oltages Over 2.048 V or Less Than 0 V onitor Temperature from Thermistor. onitor Temperature from Thermal Diode (Voltage Mode) onitor Temperature from Thermal Diode (Current Mode)  PORT UART Control Register (UCR) (Read/Write)                                       | 53565656575757585858585960616162     |

| 8.           | 6.1.3<br>6.1.4<br>EC SI<br>7.1 Fe<br>7.2 E0<br>7.2.1<br>7.2.2<br>7.2.3<br>7.2.4<br>7.2.5<br>7.2.6<br>7.2.7<br>7.2.8<br>7.3 O<br>ANAL<br>8.1 Vo<br>8.2 M<br>8.3 M<br>8.4 M<br>UART<br>9.1.1<br>9.1.2 | Exit the Extended Function Mode Software Programming Example.  PACE Beatures Implemented by Firmware C Space Register Set Page Port0 – Base Address0 + 0. Index Port0 – Base Address0 + 1. Data Port0 – Base Address0 + 2. Host Interface Event Register0 – Base Address0 + 3 Page Port1 – Base Address0 + 4. Index Port1 – Base Address0 + 5. Data Port1 – Base Address0 + 6. Host Interface Event Register1 – Base Address0 + 7 perations on EC Space OG INPUTS Ditages Over 2.048 V or Less Than 0 V onitor Temperature from Thermistor onitor Temperature from Thermal Diode (Voltage Mode) onitor Temperature from Thermal Diode (Current Mode)  PORT UART Control Register (UCR) (Read/Write) UART Status Register (USR) (Read/Write) | 535656565757575858585858585858585858 |

|     | 9.1.6            | Interrupt Status Register (ISR) (Read only)        |    |

|-----|------------------|----------------------------------------------------|----|

|     | 9.1.7            | Interrupt Control Register (ICR) (Read/Write)      | 67 |

|     | 9.1.8            | Programmable Baud Generator (BLL/BHL) (Read/Write) | 67 |

|     | 9.1.9            | User-defined Register (UDR) (Read/Write)           | 68 |

| 10. | PARAL            | LEL PORT                                           | 69 |

|     | 10.1 Pri         | nter Interface Logic                               | 69 |

|     |                  | hanced Parallel Port (EPP)                         |    |

|     | 10.2.1           | Data Port (Data Swapper)                           |    |

|     | 10.2.2           | Printer Status Buffer                              |    |

|     | 10.2.3           | Printer Control Latch and Printer Control Swapper  |    |

|     | 10.2.4           | EPP Address Port                                   |    |

|     | 10.2.5           | EPP Data Port 0-3                                  |    |

|     | 10.2.6           | EPP Pin Descriptions                               |    |

|     | 10.2.7           | EPP Operation                                      |    |

|     | 10.3 Ex          | tended Capabilities Parallel (ECP) Port            |    |

|     | 10.3.1           | ECP Register and Bit Map                           |    |

|     | 10.3.2           | Data and ecpAFifo Port                             |    |

|     | 10.3.3           | Device Status Register (DSR)                       |    |

|     | 10.3.4           | Device Control Register (DCR)                      |    |

|     | 10.3.5           | CFIFO (Parallel Port Data FIFO) Mode = 010         |    |

|     | 10.3.6           | ECPDFIFO (ECP Data FIFO) Mode = 011                |    |

|     | 10.3.7           | TFIFO (Test FIFO Mode) Mode = 110                  |    |

|     | 10.3.8           | CNFGA (Configuration Register A) Mode = 111        |    |

|     | 10.3.9           | CNFGB (Configuration Register B) Mode = 111        |    |

|     | 10.3.10          |                                                    |    |

|     | 10.3.11          | · · · · · · · · · · · · · · · · · · ·              |    |

|     | 10.3.12          | •                                                  |    |

|     | 10.3.13          | ·                                                  |    |

|     | 10.3.14          | ·                                                  |    |

|     | 10.3.15          | Programmed I/O (NON-DMA) Mode                      | 80 |

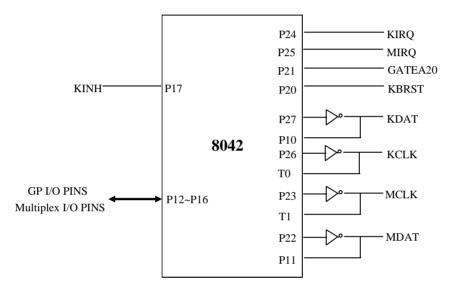

| 11. | KEYBO            | DARD CONTROLLER                                    |    |

|     |                  | tput Buffertput Buffer                             |    |

|     |                  | out Buffer                                         |    |

|     |                  | atus Register                                      |    |

|     |                  | mmands                                             |    |

|     |                  | rdware GATEA20/Keyboard Reset Control Logic        |    |

|     | 11.5.1           | KB Control Register (Logic Device 5, CR-F0)        |    |

|     | 11.5.2           | Port 92 Control Register (Default Value = 0x24)    |    |

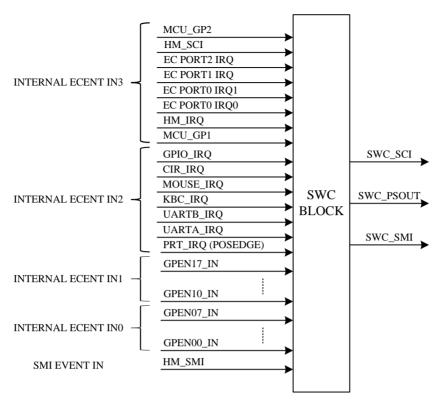

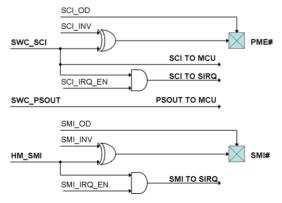

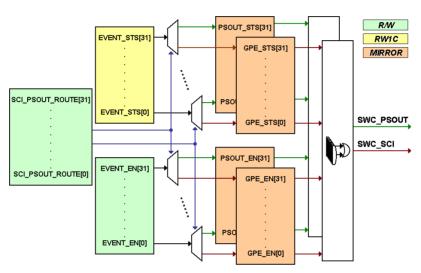

| 12. | _                | R MANAGEMENT EVENT                                 |    |

| ۱۷. | _                | stem Wakeup Control (SWC)                          |    |

|     | •                | • • • • • • • • • • • • • • • • • • • •            |    |

|     | 12.1.1           | OVERVIEW Function Description                      |    |

|     | 12.1.2<br>12.1.3 | Registers                                          |    |

| 40  | _                | -                                                  |    |

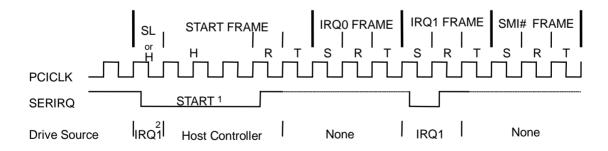

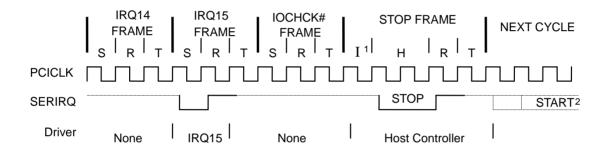

| 13. |                  | LIZED IRQ                                          |    |

|     |                  | art Frame                                          |    |

|     |                  | Q/Data Frame                                       |    |

|     | 13.3 Std         | pp Frame                                           | 99 |

| 14. | C             | ONSU                      | IMER INFRARED REMOTE (CIR)                                            | 100                  |

|-----|---------------|---------------------------|-----------------------------------------------------------------------|----------------------|

|     | 14.1          | CIR                       | Register Table                                                        | 100                  |

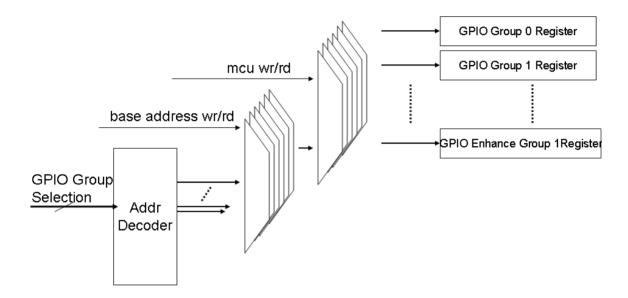

| 15. | GI            |                           | AL PURPOSE I/O                                                        |                      |

|     | 15.1          | GPI                       | O Block Diagram                                                       | 109                  |

|     | 15.2          |                           | O Runtime Register                                                    |                      |

|     | 15            | .2.1                      | GPIO Group 0 Run timer register and control register (base+0)         |                      |

|     | 15            | .2.2                      | GPIO Group 1 Run timer register and control register (base+1)         |                      |

|     | 15            | .2.3                      | GPIO Group 2 Run timer register and control register (base+2)         |                      |

|     |               | .2.4                      | GPIO Group 3 Run timer register and control register (base+3)         |                      |

|     |               | .2.5                      | GPIO Group 4 Run timer register and control register (base+4)         |                      |

|     |               | .2.6                      | GPIO Group 5 Run timer register and control register (base+5)         |                      |

|     | 15            | .2.7                      | GPIO Group 6 Run timer register and control register (base+6)         |                      |

|     | 15            | .2.8                      | GPIO Group 7 Run timer register and control register (base+7)         |                      |

|     | 15            | .2.9                      | GPIO Group 8 Run timer register and control register (base+8)         |                      |

|     | 15            | .2.10                     | GPIO Group 9 Run timer register and control register (base+9)         |                      |

|     | 15            | .2.11                     | GPIO Enhance Group 0 Run timer register and control register (base+B) |                      |

|     | 15            | .2.12                     | GPIO Enhance Group 1 Run timer register and control register (base+C) |                      |

|     | 15            | .2.13                     | GPIO SLECTION register (base+D)                                       |                      |

| 16. |               |                           | _AVE INTERFACE MODULE (ESPI_SIF)                                      |                      |

|     | 16.1          |                           | tures                                                                 |                      |

|     | 16.2          |                           | lule Interface                                                        |                      |

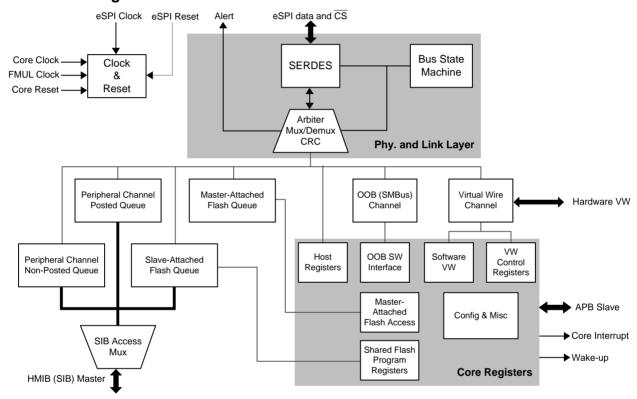

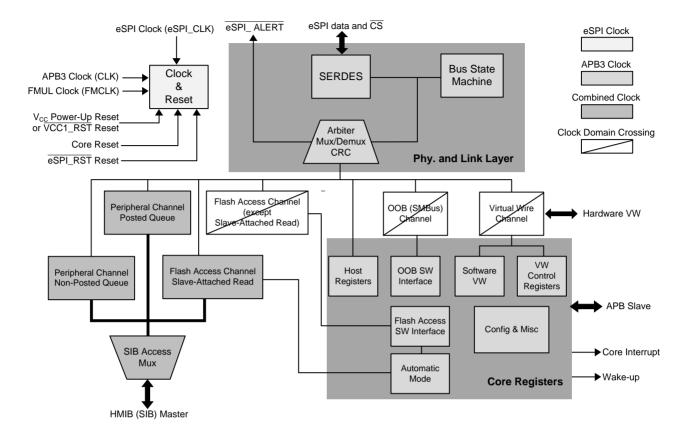

|     | 16.3          |                           | ck Diagram                                                            |                      |

|     | 16.4          |                           | cocol Layer                                                           |                      |

|     | 16.4.1        |                           | WAIT_STATE Cycles                                                     |                      |

|     | _             | .4.1<br>.4.2              | Turn-Around Cycles                                                    |                      |

|     |               | . <del>4</del> .2<br>.4.3 | Alert Indication                                                      |                      |

|     |               | .4.3<br>.4.4              | Address Decoding                                                      |                      |

|     | _             | .4.5                      | Completion Appended                                                   |                      |

|     |               | . <del>4</del> .5<br>.4.6 | Error Conditions                                                      |                      |

|     | 16.5          |                           | nsaction Layer                                                        |                      |

|     |               | .5.1                      | Peripheral Channel                                                    |                      |

|     |               | .5.1                      | Virtual Wire Channel                                                  |                      |

|     | _             | .5.2<br>.5.3              | OOB (Tunneled SMBus) Channel                                          |                      |

|     |               | .5.3<br>.5.4              | Master-Attached Flash Access Channel                                  |                      |

|     | _             | _                         |                                                                       |                      |

|     | 16.6          |                           | e Interrupt                                                           |                      |

|     | 16.7          |                           | e Wake-Up                                                             |                      |

|     | 16.8          |                           | ck                                                                    |                      |

|     | 16.9          |                           | et                                                                    |                      |

|     | 16.10         |                           | Low-Power Support                                                     |                      |

|     | 16.11         |                           | eSPI_SIF Host Registers                                               |                      |

|     | _             | .11.1                     | eSPI_SIF Host Register Map                                            |                      |

|     |               | .11.2                     | Status Register (STATUS)                                              |                      |

|     |               | .11.3                     | Device Identification Register                                        |                      |

|     |               | .11.4                     | General Capabilities and Configuration Register                       |                      |

|     |               | .11.5                     | Channel 0 Capabilities and Configuration Register                     |                      |

|     |               | .11.6                     | Channel 1 Capabilities and Configuration Register                     |                      |

|     |               | .11.7                     | Channel 2 Capabilities and Configuration Register                     |                      |

| Co  | 16<br>nfident | .11.8<br>ial              | Channel 3 Capabilities and Configuration Register                     | 137<br>Apr. 21, 2017 |

|     | ., 111        | ~~                        | IV                                                                    | 11p1.21,201/         |

|     | 16.12 | eSPI_SIF Core Registers                                                         | 138  |

|-----|-------|---------------------------------------------------------------------------------|------|

|     | 16.12 | 2.1 eSPI_SIF Core Register Map                                                  | .139 |

|     | 16.12 | 2.2 eSPI Identification Register (ESPIID)                                       | .139 |

|     | 16.12 |                                                                                 |      |

|     | 16.12 | 2.4 eSPI Status Register (ESPISTS)                                              | .143 |

|     | 16.12 | 2.5 eSPI Interrupt Enable Register (ESPIIE)                                     | .145 |

|     | 16.12 | 2.6 Virtual Wire Register Index Register (VWREGIDX)                             | .146 |

|     | 16.12 | 2.7 Virtual Wire Register Data Register (VWREGDATA)                             | .147 |

|     | 16.12 | 2.8 OOB Channel Control Register (OOBCTL)                                       | .147 |

|     | 16.12 | 2.9 Flash CRC/Checksum Register (FLASHCRC) - Not Used                           | .148 |

|     | 16.12 | 2.10 Flash Channel Configuration Register (FLASHCFG)                            | .148 |

|     | 16.12 | 2.11 Flash Channel Control Register (FLASHCTL)                                  | .150 |

|     | 16.12 | 2.12 eSPI Error Status Register (ESPIERR)                                       | .151 |

|     | 16.12 | 2.13 Virtual Wire Event Register Reset Values                                   | .153 |

|     | 16.12 | 2.14 Virtual Wire Event Slave-to-Master Register n (VWEVSMn), n = 0 - 9         | .154 |

|     | 16.12 |                                                                                 |      |

|     | 16.12 | 2.16 Virtual Wire Event Slave-to-Master Type Register n (VWEVSMTYPE)            | .156 |

|     | 16.12 |                                                                                 |      |

|     | 16.12 | 2.18 Virtual Wire Channel Control Register (VWCTL)                              | .158 |

|     | 16.12 |                                                                                 |      |

|     | 16.12 | 2.20 OOB Transmit Buffer Register n (OOBTXBUFn), n = 0-19                       | .158 |

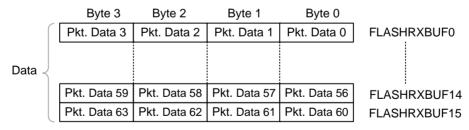

|     | 16.12 | 2.21 Flash Receive Buffer Register n, (FLASHRXBUFn), n = 0-16                   | .159 |

|     | 16.12 | 2.22 Flash Transmit Buffer Register n, (FLASHTXBUFn), n = 0-5                   | .159 |

|     | 16.13 | eSPI_SIF Integration Implementation Notes                                       | 160  |

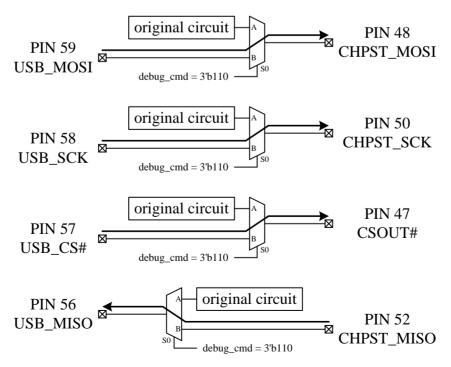

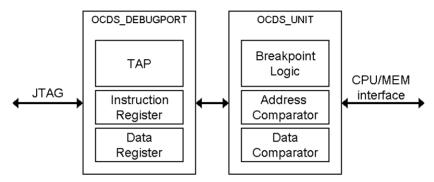

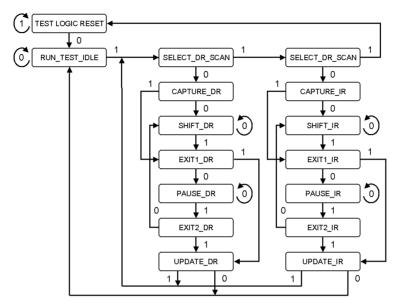

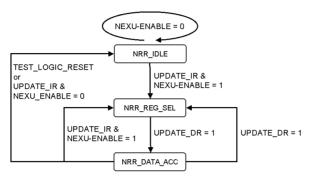

| 17. | ON-0  | CHIP DEBUG SUPPORT INTERFACE (ODCS)                                             |      |

|     |       | Overview                                                                        |      |

|     |       | Function Description                                                            |      |

|     | 17.2. | ·                                                                               |      |

|     | 17.2. |                                                                                 |      |

|     | 17.2. |                                                                                 |      |

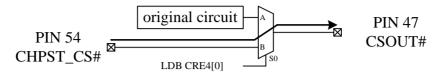

| 18. |       | IFIGURATION REGISTER                                                            |      |

| ٠٠. |       | Chip (Global) Control Register                                                  |      |

|     |       | Logical Device 1 (Parallel Port)                                                |      |

|     |       | Logical Device 2 (UARTA)                                                        |      |

|     |       | • ,                                                                             |      |

|     |       | Logical Device 3 (UARTB, IR)                                                    |      |

|     |       | Logical Device 5 (Keyboard Controller)                                          |      |

|     |       | Logical Device 6 (CIR)                                                          |      |

|     |       | Logical Device 7 (GPIO0~GPIO7)                                                  |      |

|     |       | Logical Device 8 (PORT80 UART)                                                  |      |

|     |       | Logical Device 9 (GPIO8~9, GPIO 1~8 Alternate Function, GPIO Enhance Group 0~1) |      |

|     | 18.10 | Logical Device A (ACPI)                                                         |      |

|     | 18.11 | Logical Device B (EC Space)                                                     |      |

|     | 18.12 | Logical Device C (RTC Timer)                                                    | 237  |

|     | 18.13 | Logical Device D (Deep Sleep, Power Fault)                                      | 242  |

|     | 18.14 | Logical Device E (TACHIN/PWMOUT Assignment)                                     | 250  |

|     | 18.15 | Logical Device F (Function Register)                                            | 254  |

| 19. | SPE   | CIFICATIONS                                                                     | 256  |

|     | 19.1 Absolute Maximum Ratings |           |                                                    |     |  |  |  |  |  |

|-----|-------------------------------|-----------|----------------------------------------------------|-----|--|--|--|--|--|

|     | 19.2                          | DC        | CHARACTERISTICS                                    |     |  |  |  |  |  |

| 20. | AC                            | CHA       | ARACTERISTICS                                      | 259 |  |  |  |  |  |

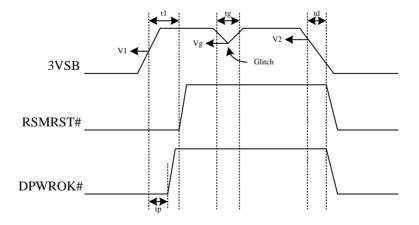

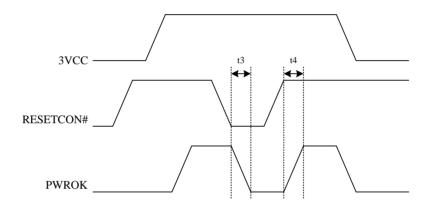

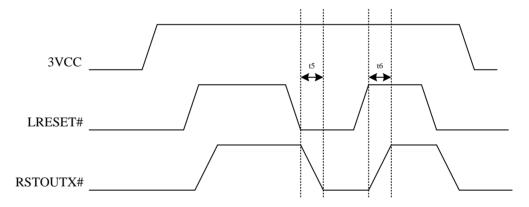

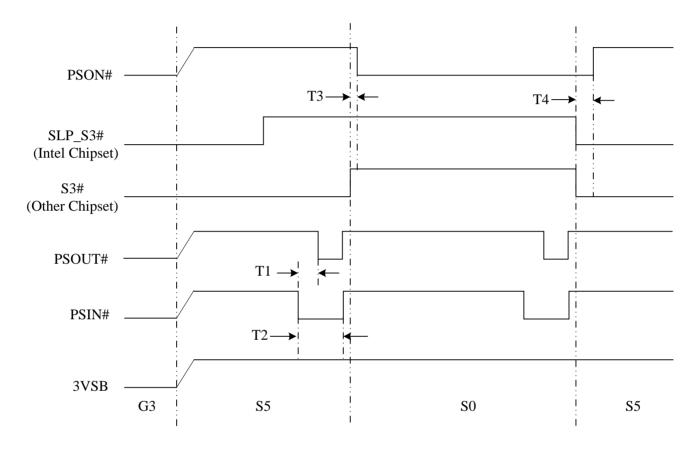

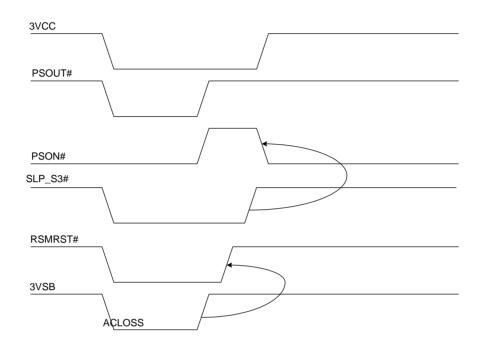

|     | 20.1                          | Pow       | ver On / Off Timing                                | 259 |  |  |  |  |  |

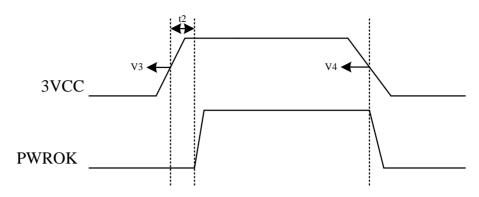

|     | 20.2                          | AC        | Power Failure Resume Timing                        | 260 |  |  |  |  |  |

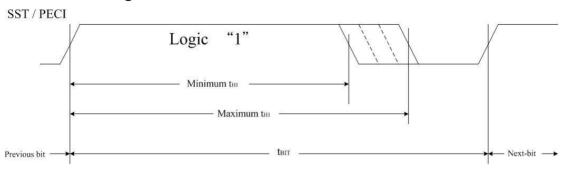

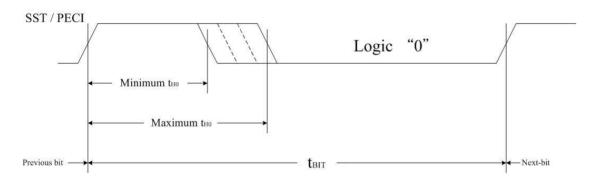

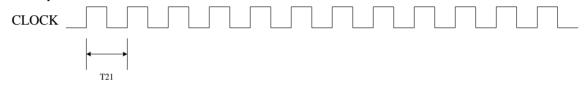

|     | 20.3                          | CI Timing | 263                                                |     |  |  |  |  |  |

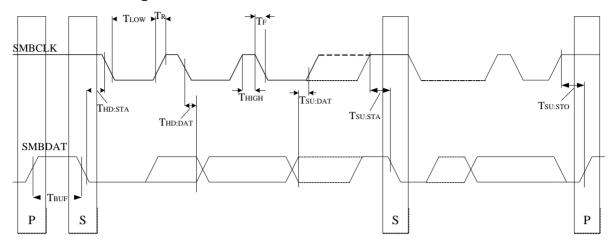

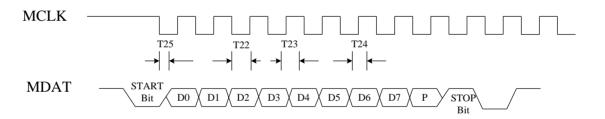

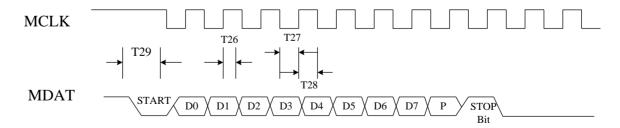

|     | 20.4                          | SMI       | Bus Timing                                         | 264 |  |  |  |  |  |

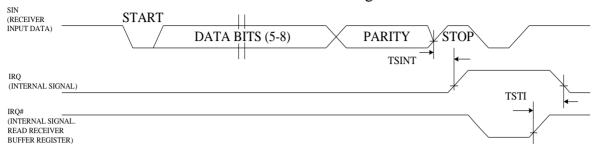

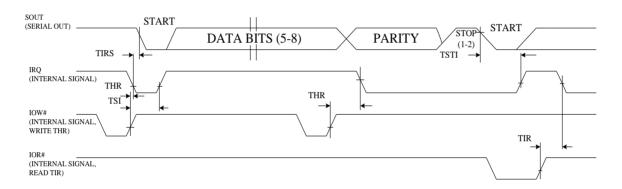

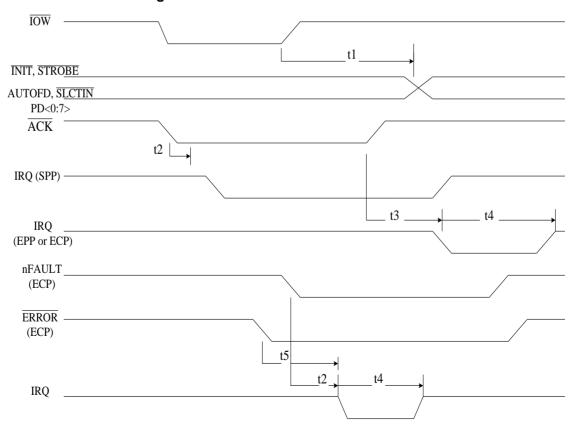

|     | 20.5                          | UAF       | RT/Parallel Port                                   | 264 |  |  |  |  |  |

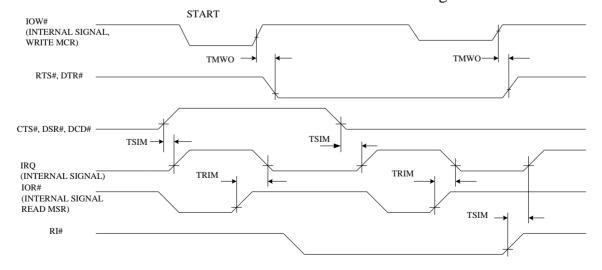

|     | 20.6                          | Mod       | dem Control Timing                                 | 265 |  |  |  |  |  |

|     | 20.7                          | Para      | allel Port Mode Parameters                         | 266 |  |  |  |  |  |

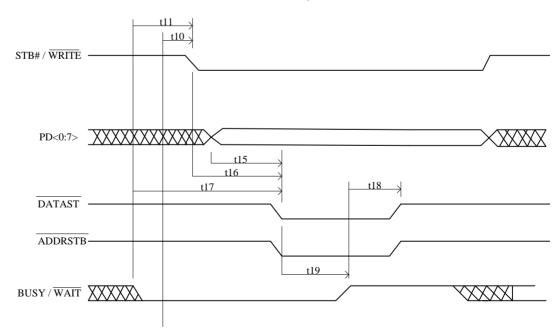

|     | 20.7                          | 7.1       | Parallel Port Timing                               | 266 |  |  |  |  |  |

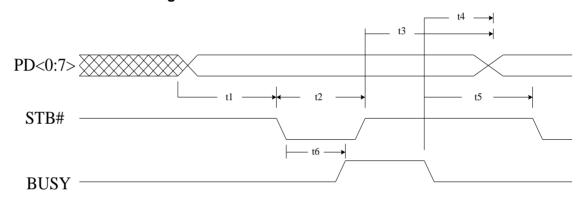

|     | 20.7                          | 7.2       | EPP Data or Address Read Cycle Timing Parameters   | 267 |  |  |  |  |  |

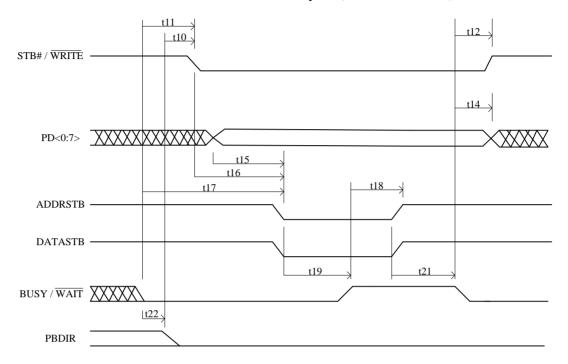

|     | 20.7                          | 7.3       | EPP Data or Address Read Cycle (EPP Version 1.9)   | 268 |  |  |  |  |  |

|     | 20.7                          | 7.4       | EPP Data or Address Read Cycle (EPP Version 1.7)   | 269 |  |  |  |  |  |

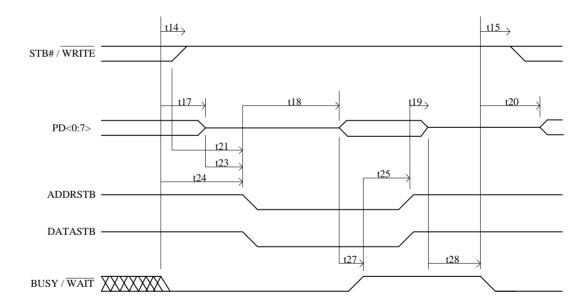

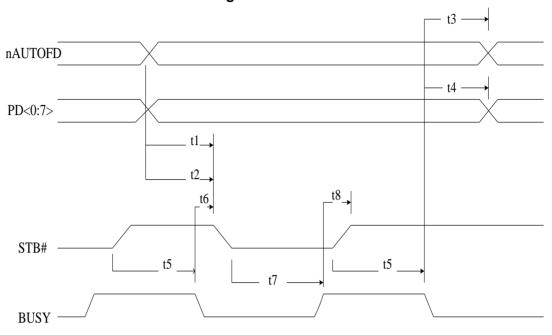

|     | 20.7                          | 7.5       | EPP Data or Address Write Cycle Timing Parameters  |     |  |  |  |  |  |

|     | 20.7                          |           | EPP Data or Address Write Cycle (EPP Version 1.9)  |     |  |  |  |  |  |

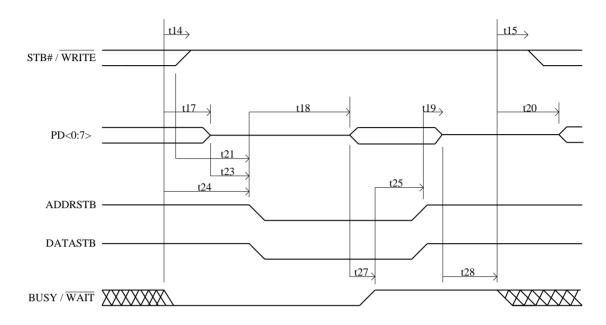

|     | 20.7                          |           | EPP Data or Address Write Cycle (EPP Version 1.7)2 |     |  |  |  |  |  |

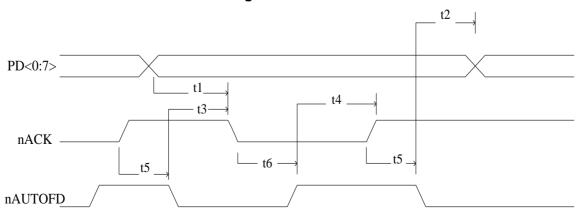

|     | 20.7                          | -         | Parallel Port FIFO Timing Parameters               |     |  |  |  |  |  |

|     | 20.7                          | -         | Parallel FIFO Timing                               |     |  |  |  |  |  |

|     | _                             | 7.10      | ECP Parallel Port Forward Timing Parameters        |     |  |  |  |  |  |

|     | _                             | 7.11      | ECP Parallel Port Forward Timing                   |     |  |  |  |  |  |

|     | _                             | 7.12      | ECP Parallel Port Reverse Timing Parameters        |     |  |  |  |  |  |

|     |                               | 7.13      | ECP Parallel Port Reverse Timing                   |     |  |  |  |  |  |

|     | 20.8                          |           | C Timing Parameters                                |     |  |  |  |  |  |

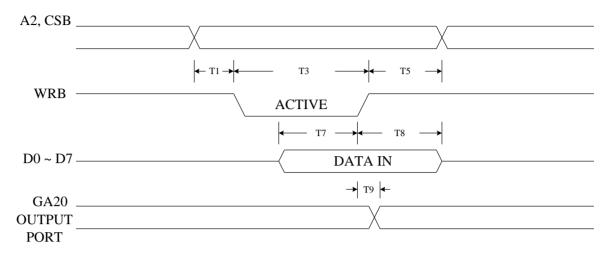

|     | 20.8                          | _         | Writing Cycle Timing                               |     |  |  |  |  |  |

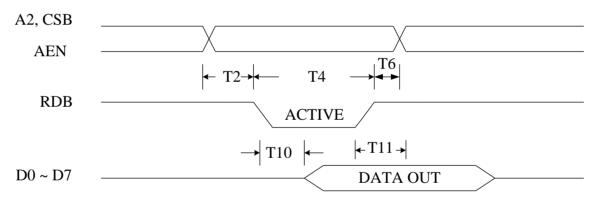

|     | 20.8<br>20.8                  | _         | Read Cycle Timing                                  |     |  |  |  |  |  |

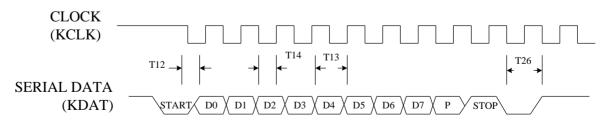

|     | 20.8                          |           | Receive Data from K/B                              |     |  |  |  |  |  |

|     | 20.8                          | _         | Input Clock                                        |     |  |  |  |  |  |

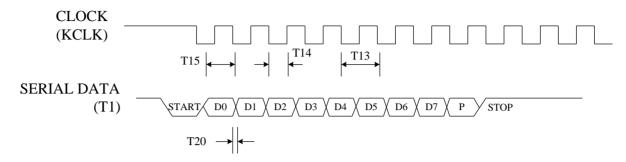

|     | 20.8                          |           | Send Data to Mouse                                 |     |  |  |  |  |  |

|     | 20.8                          |           | Receive Data from Mouse                            |     |  |  |  |  |  |

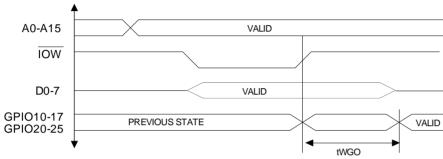

|     | 20.9                          | -         | O Timing Parameters                                |     |  |  |  |  |  |

|     | 20.9                          |           | GPIO Write Timing                                  |     |  |  |  |  |  |

| 21. |                               |           | ARKING SPECIFICATIONS                              |     |  |  |  |  |  |

| 22. |                               |           | RING INFORMATION                                   |     |  |  |  |  |  |

| 23. |                               |           | GE SPECIFICATION                                   |     |  |  |  |  |  |

| 24. |                               |           | ON HISTORY                                         |     |  |  |  |  |  |

| ∠⊤. | 11                            | 4 1 O I   | ♥! ₹ ! !!♥! ♥! ₹                                   |     |  |  |  |  |  |

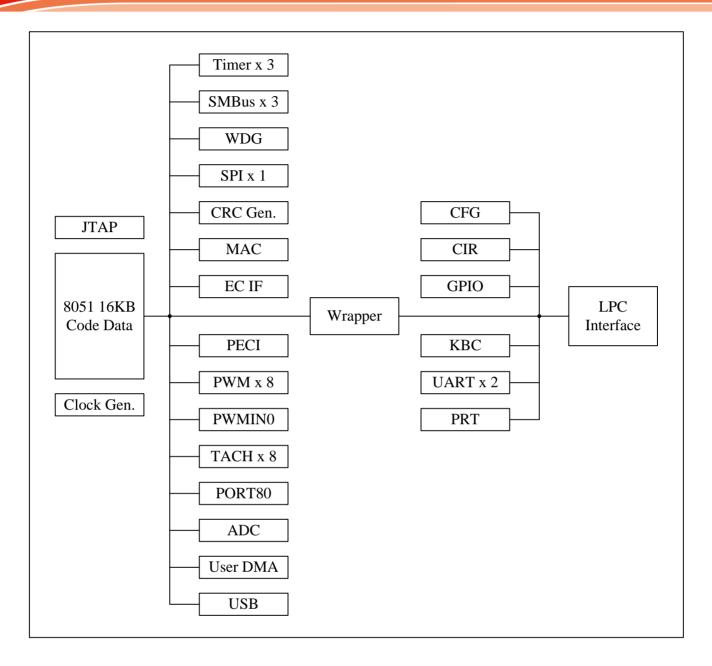

#### 1. GENERAL DESCRIPTION

NCT6686D is a high performance 8 bit microcontroller to execute MCS51 instruction set. A rich set of features and peripherals enable to match many specific applications, for example, PC mother board Super IO, Notebook/Netbook EC controller or consumer health monitor embedded controller.

The microcontroller includes memory pointer, interrupts, interfaces for serial communication, I2C and SPI interfaces, a timer system, I/O ports, power management unit, multiplication-division unit, watchdog timer and DMA controller. Integrated on-chip debugger is also available.

NCT6686D provides flexible I/O control functions through a set of general purpose I/O (GPIO) ports. These GPIO port may serve as simple I/O ports or may be individually configured to provide alternative functions. The GPIO can be programmed to generate interrupt microcontroller. Also the GPIO can be programmed to generate flexible power-on sequence for different CPU and chipset.

NCT6686D monitors several critical parameters in hardware, including power supply voltages, fan speeds, and temperatures. In terms of temperature monitoring, NCT6686D adopts the Current Mode (dual current source) and thermistor sensor approach, as well as PECI (Platform Environment Control Interface) and AMD SB-TSI interface. NCT6686D also supports the Smart Fan control system, including "SMART FAN<sup>TM</sup> I and SMART FAN<sup>TM</sup> III and SMART Tracking, which makes the system more stable and user-friendly.

NCT6686D supports SMBus host/slave function. As a master, it could access multiple slave devices; as a slave, it could be accessed for reporting useful information.

NCT6686D provides an USB host interface to connect to USB device. Different kinds of USB application could be implemented by firmware.

NCT6686D provides two high-speed serial communication ports (UART), each of them includes a 16-byte send/receive FIFO, a programmable baud rate generator, complete modem-control capability, and a processor interrupt system. The UART supports legacy speeds up to 115.2K bps as well as even higher baud rates of 230K, 460K or 921K bps to support higher speed moderms.

NCT6686D supports the PC-compatible printer port (SPP), the bi-directional printer port (BPP), the enhanced parallel port (EPP) and the extended capabilities port (ECP).

#### 2. FEATURES

- 1 T XC8051

- 16K bytes of data RAM

- MCU runs on EXTERNAL serial program storage (NOR Flash with SPI interface) on the fly directly. Address space up to 16M bytes was supported.(23-bit addressing).

- MCU interrupt on various system events, to enable glue logic enhancements and customization

- Access to any of NCT6686D registers to provide:

- --- Control over the SIO pin selection.

- --- Control over the configuration of any NCT6686D function or devices.

- --- Control and monitoring of any GPIO pin

- Peripherals

- --- 2 serial ports

- --- 3 timer counters

- --- Internal watchdog timer

- --- SMBus Interfaces used for:

- Master: Temperature reading

- Slave : Providing infrastructure for MCTP/PLDM and ASF-based manageability

- Slave : Remote access to the device registers

- --- SPI interfaces

- code fetch of NCT6686D execution

- --- USB interface

- 14.318 MHz operation clock with crystal input (Xin / Xout)

- Adjustable internal clock for various utilizations

- Flexible ISP (In-System-Program) Interfaces

- --- LPC Bus

- --- eSPI Bus

- --- SPI (from KBMS pin)

#### **System Hardware Management Support**

- Digital Thermal interfaces

- --- PECI 3.0 for Intel CPU thermal monitoring and support up to address 8 CPUs and 2 domains

- --- SB-TSI 1.0/APML for AMD CPU thermal monitoring

- --- SMBus devices.

- Local and remote Thermal measurement sensors

- --- external Thermal Diode or Thermistor monitor interfaces

- --- internal Thermal measurement diode

- Incorporates 8-bit analog-to-digital converter

- --- Analog inputs filtering

- --- Firmware-based digital filtering

- --- Remote thermal sensing designed for typical precision of 1 °C.

- --- 0.125 °C resolution.

- Fan Monitor and Control

- --- Adaptive fan control algorithm

- --- 8 PWM-based output fan controls

- --- Up to 8 fan speed monitoring inputs with 12-bit resolution tachometers

- --- Automatic temperature feedback control.

- Generates SMI on critical temperature events

- Voltage Monitoring

- --- Up to 10 VIN

- --- VSB, AVSB, VCC3

- --- VBAT

#### **General Purpose I/O Ports**

- GPIO pins can be used either by the MCU or by the host

- · All GPIO pins individually configured as input or output

- Programmable features for each output pin:

- --- Drive type (open-drain, push-pull or TRI-STATE

- --- TRI-STATE condition on detection of falling VDD3 for VSB3-powered pins driving VDD-supplied devices

- Programmable option for internal pull-up resistor on some input pin (some with internal pulldown resistor option)

- · Lock option for the configuration and data of each GPIO port

- 16 pins can generate MCU interrupt events for the internal microcontroller

- GPIO pins generate IRQ/SIOPME/SMI for wake-up events. Each GPIO has separate:

- --- Enable control of event status routing to IRQ (For Each GPIO Input)

- --- Enable control of event status routing to SIOPME (Only for GPIO Enhance port)

- --- Polarity and edge/level selection

- --- Optional de-bouncing

#### **Diagnostics**

- High current driver power indicator LED blinking

- --- Dual Color Control

- --- Fading Mode

- Support two ports for Port80-like message output. Each port supports two digits.

- --- Directly drive 7-Segment LEDs

- --- The decode port is configurable.

- --- To save pin counts, it would be better to support 4 digits with same 7 data pins(LEDA~LEDG).

- --- Through UART port

#### Fail-safe ACPI and Optional Firmware-Enhanced Features (Control through EC Space)

- ACPI power sequence controls and glue logics, such as RSMRST#, PSON#, PWROK0, RSTOUT0#, PSIN, PSOUT#, ATXPGD, SLP\_S3#, SLP\_S5#,

- --- Main Power good / power OK signals ATXPGD and internal power sensing.

- --- Power distribution control (for switching between Main and Standby regulators)

- --- Main power supply turn on (PSON#)

- --- Resume reset (Master Reset) according to the stand-by 3V

- --- Reset button de-bouncer

- --- Power Good out mechanism using ATXPGD and internal power sensing

- --- Buffers PCI\_RESET to generate 3 reset output signals

- · Power restoring policy when AC was recovered

- Advanced watch dog timers

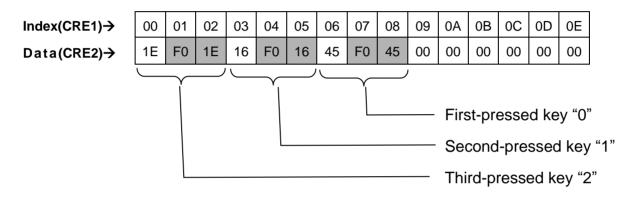

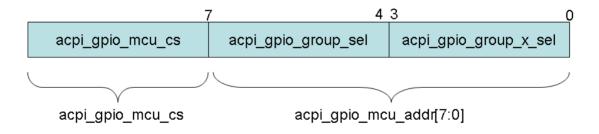

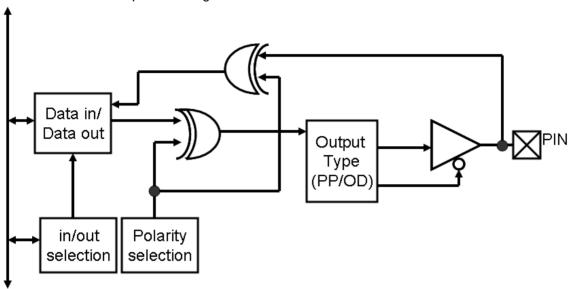

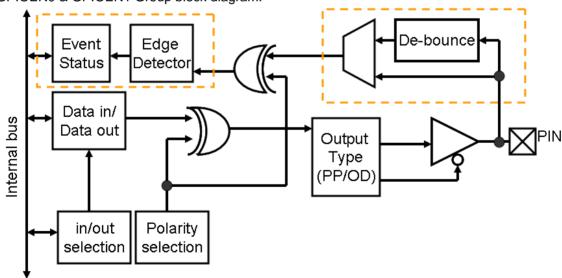

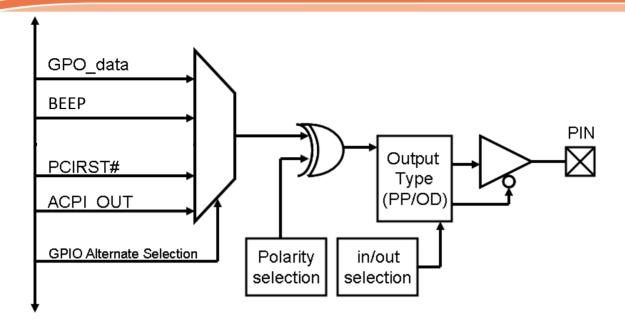

- Hardware Monitoring (including voltage sources, analog / digital / virtual temperature sources, and tachometers)