# Mixed Signal MCU MD6601 **Data Sheet**

Ant Recalling Mended for New Designation

| MD6601 Data Sheet  | Rev. 1.0                 |  |

|--------------------|--------------------------|--|

| Date of issue      | 2014.03.06               |  |

| Publication        | SANKEN ELECTRIC CO.,LTD. |  |

| Editing            | SANKEN ELECTRIC CO.,LTD. |  |

| Copyright (C) 2014 | SANKEN ELECTRIC CO.,LTD. |  |

## **CONTENTS**

| 1.  | Product Overview                                                    | 1-1      |

|-----|---------------------------------------------------------------------|----------|

|     | 1.1 Features                                                        | 1-1      |

|     | 1.1.1 Analog Sub System                                             | 1-1      |

|     | 1.1.2 Digital Sub System                                            | 1-1      |

|     | 1.2 Description                                                     | 1-3      |

|     | 1.3 Application                                                     | 1-3      |

|     | 1.4 Ordering Information                                            | 1-3      |

| 2.  | Block Diagram                                                       | <u> </u> |

|     | Pin Description                                                     | (A) 2-1  |

| 3.  | Pin Description                                                     | 3-I      |

|     | 3.1 Pin Arrangement                                                 | 2.2      |

|     | 3.2 Signal Description  Reset System and Low Voltage Detector (LVD) | 3-2      |

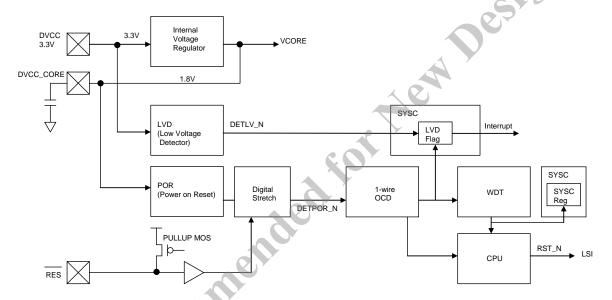

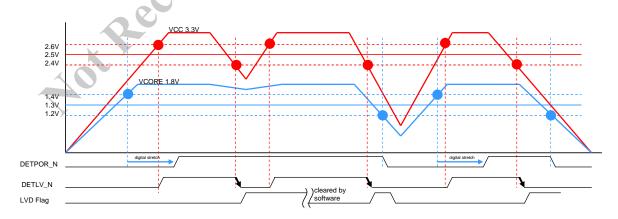

| 4.  | Reset System and Low Voltage Detector (LVD)                         | 4-1      |

|     | 4.1 Overview                                                        |          |

|     | 4.2 Register Description                                            | 4-2      |

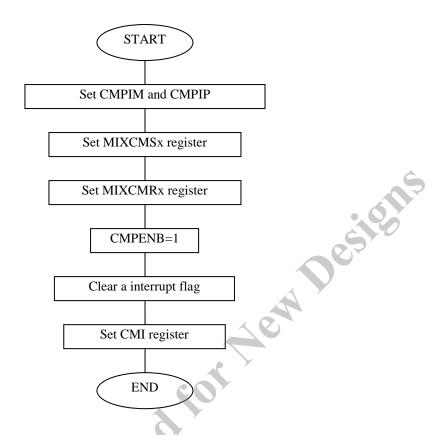

|     | 4.2.1 Detect low power-supply voltage                               | 4-2      |

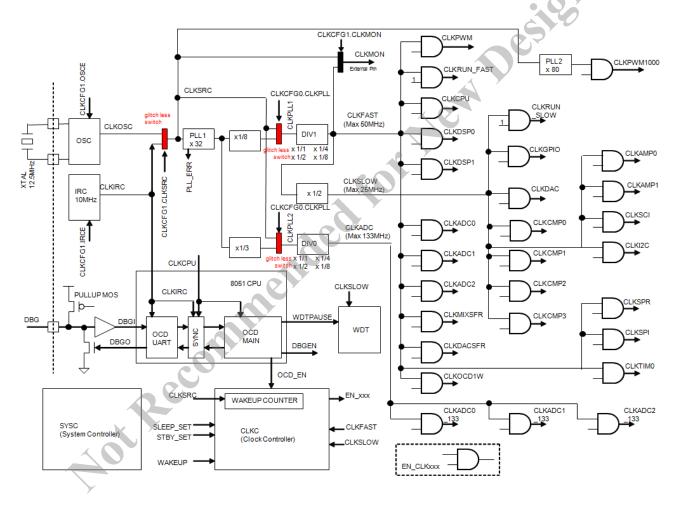

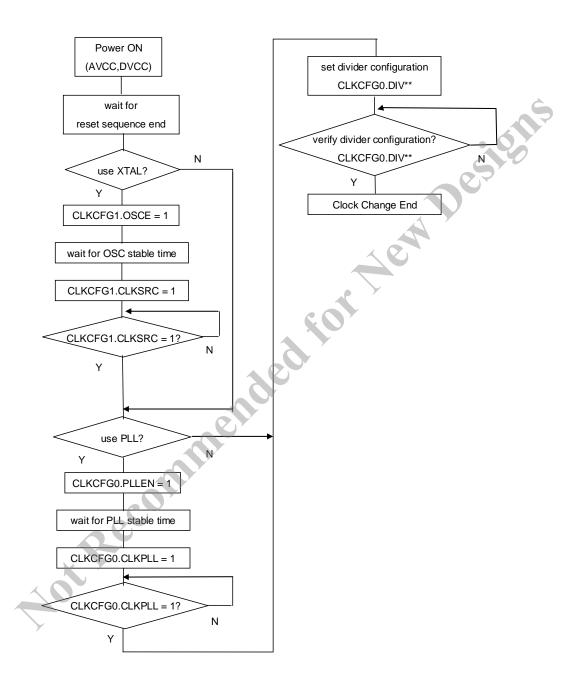

| 5.  | Clock System 5.1 Overview                                           | 5-1      |

|     | 5.1 Overview                                                        | 5-1      |

|     | 5.2 Register Description                                            | 5-2      |

|     | 5.2 Register Description 5.2.1 Clock controller                     | 5-2      |

|     | 5.2.2 Low Power Controller                                          | 5-5      |

|     | 5.3 Clock Initialization Sequence                                   | 5-5      |

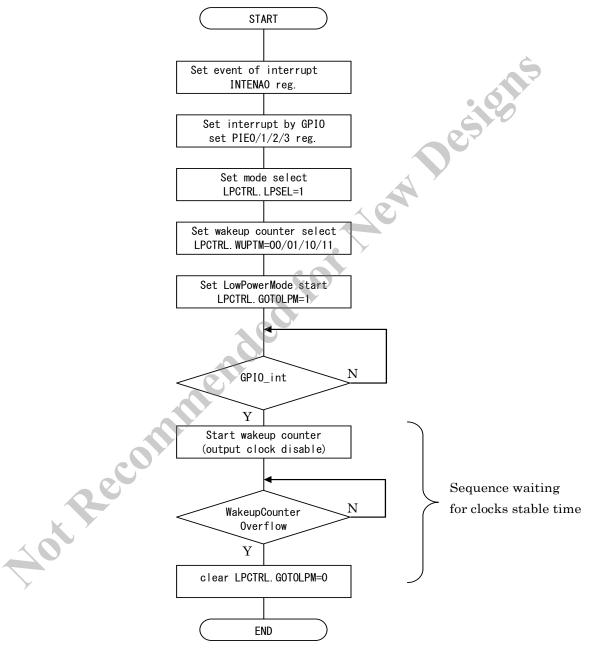

|     | 5.4 Low Power Mode                                                  |          |

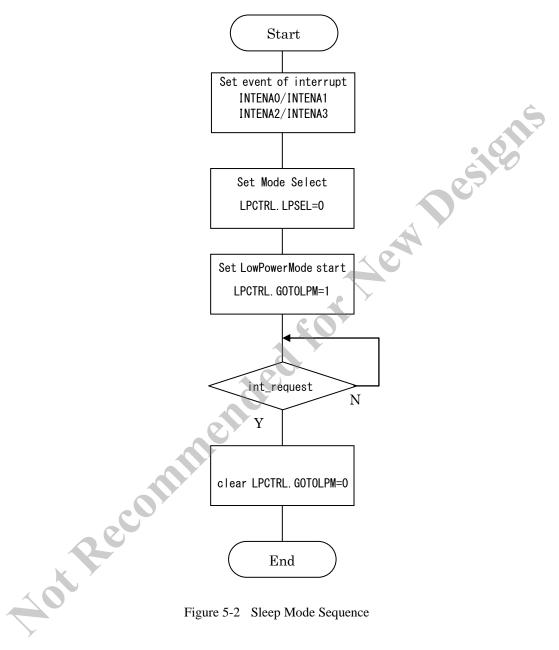

|     | 5.4.1 SLEEP Mode                                                    | 5-6      |

|     | 5.4.2 STBY Mode                                                     | 5-7      |

|     | 5.5 An example way to configure Clock Settings after Power On       | 5-8      |

|     | 5.6 Limitation of Clock System                                      | 5-9      |

|     | 5.6.1 Limitation of Low Power Mode                                  | 5-9      |

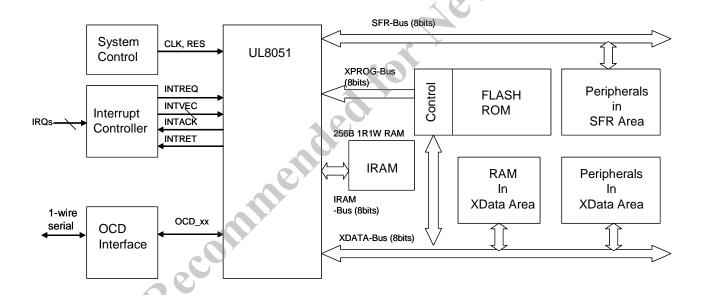

| 6.  | 8051 CPU Subsystem                                                  | 6-1      |

|     | 6.1 Introduction                                                    |          |

|     | 6.2 Overview                                                        | 6-1      |

|     | 6.3 System Configuration around CPU                                 | 6-2      |

|     | 6.4 Memory Map                                                      | 6-3      |

|     | 6.5 Register Description                                            | 6-5      |

|     | 6.5.1 Remap Control (REMAP)                                         | 6-5      |

|     | 6.6 Instruction Code Map                                            | 6-6      |

|     | 6.6.1 Notes on Instruction Spec                                     | 6-7      |

|     | 6.6.2 CPU Instruction Execution Cycle                               | 6-8      |

| 7.  | Register Mapping                                                    | 7-1      |

| , . | 7.1 Peripherals on XDATA-Bus                                        |          |

|     | 7.2 Peripherals on SFR-Bus                                          |          |

|     | 7.3 Scratch Pad Register                                            |          |

| 0   |                                                                     | . 0      |

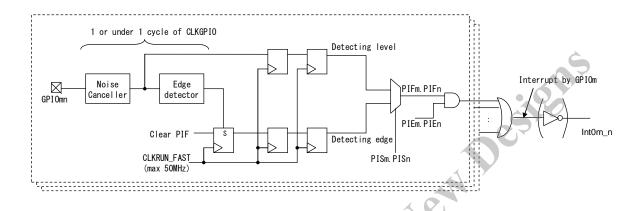

| 8.  | GPIO 8-1 8.1 GPIO Structure                                         | 0 1      |

|     | 8.1 GPIO Structure                                                  | · 8-1    |

|     | 8.2 Regi     | ster Description                                                                         | 0.2   |

|-----|--------------|------------------------------------------------------------------------------------------|-------|

|     | Ü            | •                                                                                        |       |

|     | 8.2.1        | Pin Function Select for GPIO0 (PFS0)                                                     |       |

|     | 8.2.2        | Pin Function Select for GPIOn (PFSn) (n=1-3)                                             |       |

|     | 8.2.3        | Pin Data Direction for GPIOn (PDDn) (n=0-3)                                              |       |

|     | 8.2.4        | Pin Data for GPIOn (PDRn) (n=0-3)                                                        |       |

|     | 8.2.5        | Pin Pull Up Control for GPIOn (PPUn) (n=0-3)                                             |       |

|     | 8.2.6        | Pin Interrupt Enable for GPIOn (PIEn) (n=0-3)                                            |       |

|     | 8.2.7        | Pin Interrupt Flag for GPIOn (PIFn) (n=0-3)                                              |       |

|     | 8.2.8        | Pin Interrupt Sense for GPIOn (PISn) (n=0-3)                                             |       |

|     | 8.2.9        | Pin Interrupt Level for GPIOn (PILn) (n=0-3)                                             |       |

|     | 8.2.10       | Pin Interrupt Both Edge for GPIOn (PIBn) (n=0-3)                                         | 8-8   |

|     | 8.2.11       | ADC Event Select from GPIOn (PEADCn) (n=0-3)PWM Event Select from GPIOn (PEPWMn) (n=0-3) | 8-9   |

|     | 8.2.12       | PWM Event Select from GPIOn (PEPWMn) (n=0-3)                                             | 8-9   |

|     | 8.2.13       | PWM Event Gathering Method (PEMETHOD)ections in the LSI                                  | 8-10  |

| 0   | E C          |                                                                                          | 0.1   |

| 9.  | Event Conne  | ections in the LSI                                                                       | 9-1   |

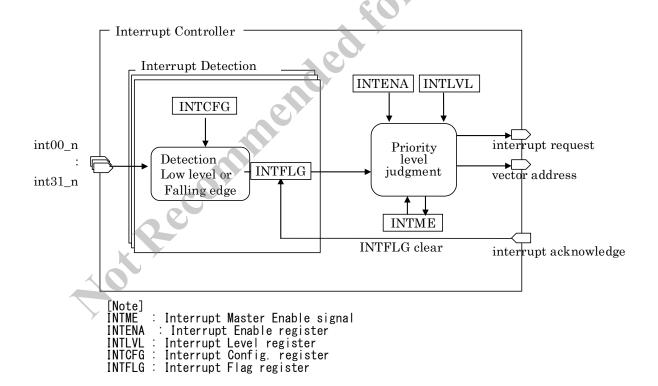

| 10. | Interrupt Co | ntroller                                                                                 | 10-1  |

|     | 10.1 Over    | viewrupt Vectors                                                                         | 10-1  |

|     | 10.2 Inter   | rupt Vectors                                                                             | 10-2  |

|     | 10.3 Regi    | ster Description                                                                         | 10-3  |

|     | 10.3.1       | INTMST                                                                                   | 10-3  |

|     | 10.3.2       | INTENA                                                                                   | 10-4  |

|     | 10.3.3       | INTLVL                                                                                   | 10-4  |

|     | 10.3.4       | INTCFG                                                                                   | 10-5  |

|     | 10.3.5       | INTFLG                                                                                   | 10-5  |

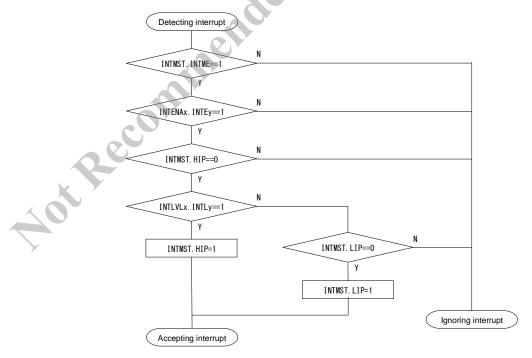

|     | 10.4 Oper    | ration                                                                                   | 10-6  |

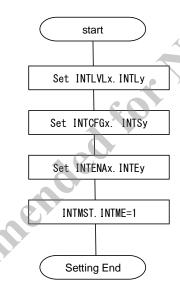

|     | 10.4.1       | Initial setting                                                                          | 10-6  |

|     |              | Interrupt flag                                                                           |       |

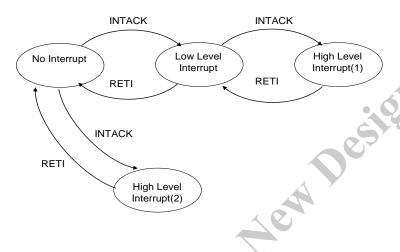

|     |              | Interrupt level                                                                          |       |

|     |              | Interrupt of external pins                                                               |       |

|     |              |                                                                                          |       |

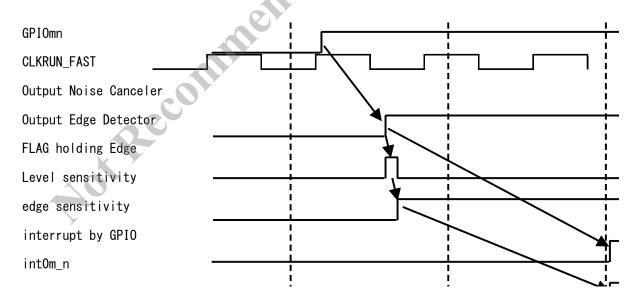

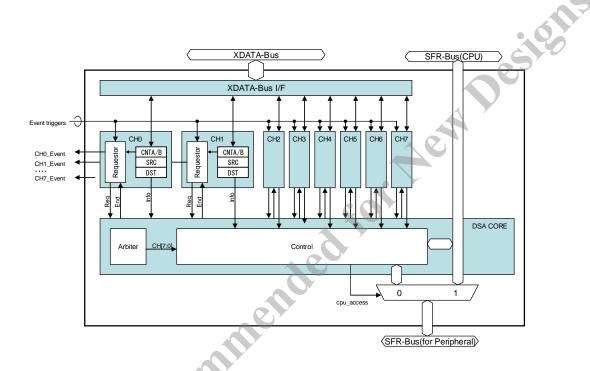

| 11. |              | ect SFR Access Controller)                                                               |       |

|     |              | view                                                                                     |       |

|     |              | ut                                                                                       |       |

|     | _            | ster Description                                                                         |       |

|     |              | DSACNTAn (DSAC Control A Register)                                                       |       |

|     |              | DSACNTBn (DSAC Control B Register)                                                       |       |

|     | 7            | DSASRCn (DSAC Source address Register)                                                   |       |

|     |              | DSADSTn (DSAC Destination address Register)                                              |       |

|     | -            | ration                                                                                   |       |

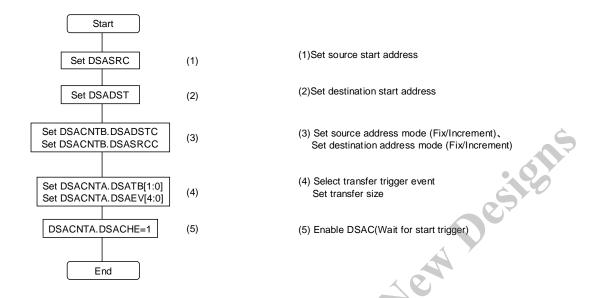

|     | 11.5 Initia  | alization sequence                                                                       | 11-8  |

|     | 11.6 Limi    | tation of DSAC                                                                           | 11-8  |

|     | 11.6.1       | Disabling DSAC                                                                           | 11-8  |

| 12  | FI ASH Ma    | mory Control                                                                             | 12 1  |

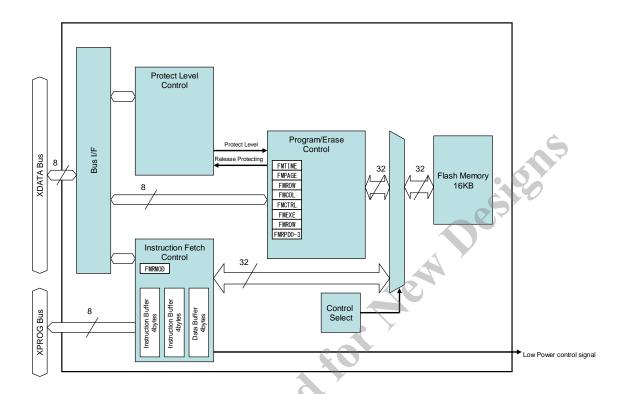

| 14. |              | view                                                                                     |       |

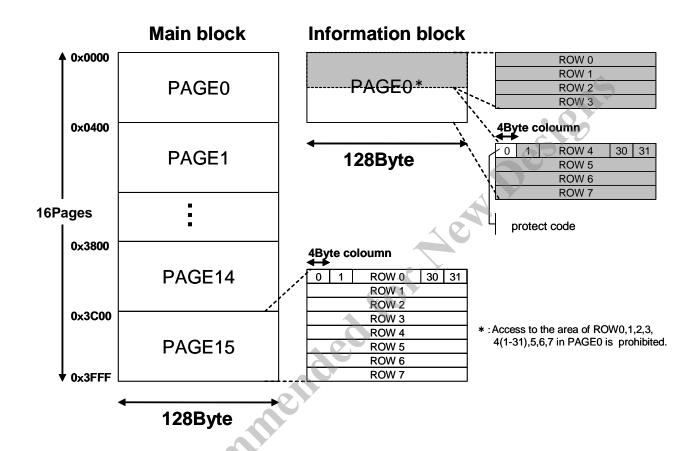

|     |              | n memory mat structure                                                                   |       |

|     |              | ster Description                                                                         |       |

|     | _            | FMTIME                                                                                   |       |

|     | 14.7.1       | 1 191 1 119112                                                                           | 1 Z-4 |

|     | 12.3.2 FMPAGE                                                     | 12-5  |

|-----|-------------------------------------------------------------------|-------|

|     | 12.3.3 FMROW                                                      | 12-5  |

|     | 12.3.4 FMCOL                                                      | 12-6  |

|     | 12.3.5 FMCTRL                                                     | 12-6  |

|     | 12.3.6 FMEXE                                                      | 12-7  |

|     | 12.3.7 FMRPD0-3                                                   | 12-8  |

|     | 12.3.8 FMRMOD                                                     | 12-8  |

|     | 12.4 Operation                                                    | 12-9  |

|     | 12.4.1 Instruction fetch                                          | 12-9  |

|     | 12.4.2 Flash programming                                          | 12-9  |

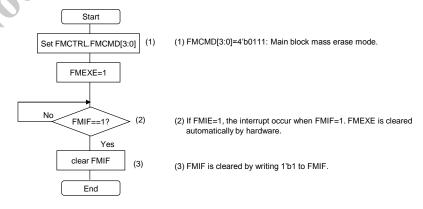

|     | 12.4.2.1. Mass Erase                                              |       |

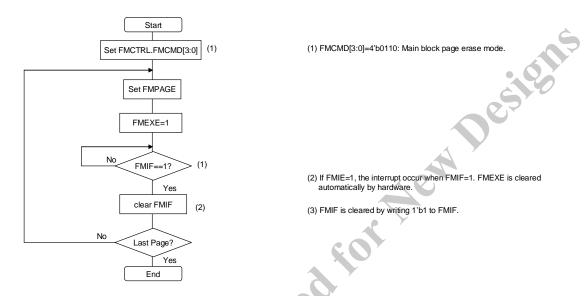

|     | 12.4.2.2. Page Erase                                              | 12-10 |

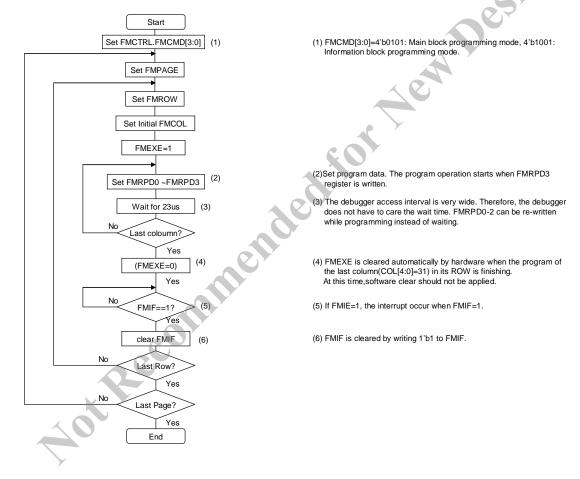

|     | 12.4.2.3. Row Programming                                         |       |

|     |                                                                   |       |

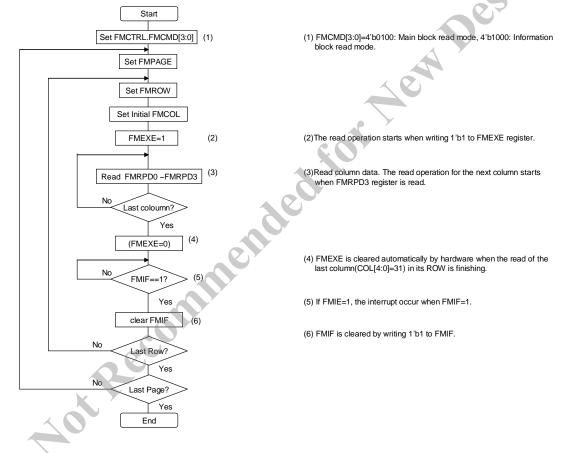

|     | 12.4.2.4. Row Data Read                                           | 12-13 |

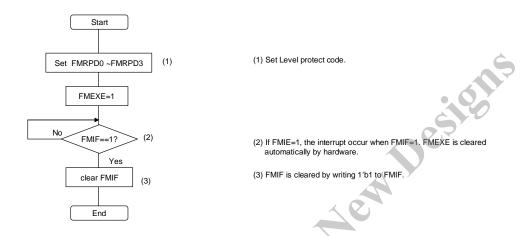

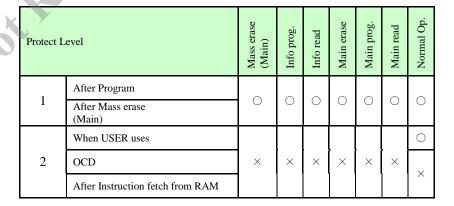

|     | 12.5 Flash protecting level control                               | 12-13 |

|     | 12.6 Limitation of FLC                                            | 12-14 |

|     | 12.6.1 Going to low power mode                                    | 12-14 |

|     | 12.6.2 Clock frequency for flash program                          | 12-14 |

|     | 12.6.3 Row programming time                                       |       |

|     |                                                                   |       |

|     | 12.6.4 Protect function  Tiny DSP                                 | 10.1  |

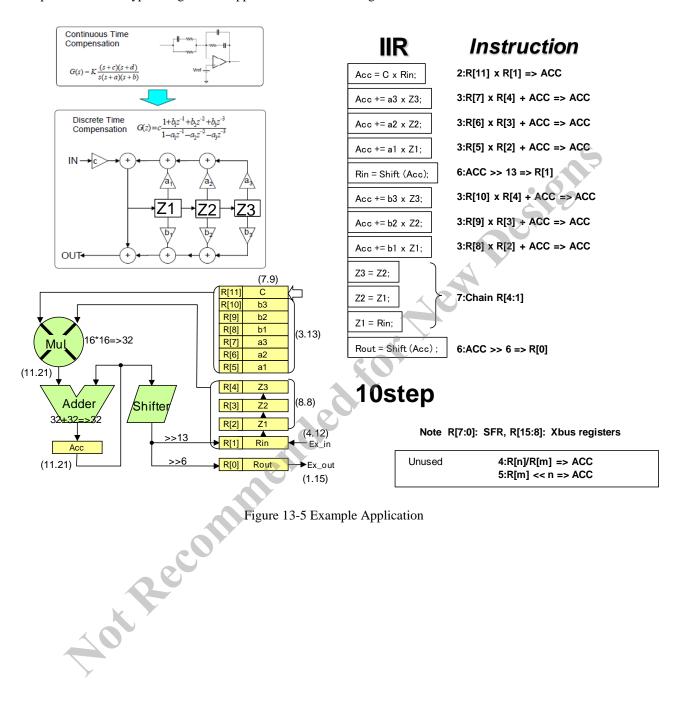

| 13. |                                                                   | 13-1  |

|     |                                                                   |       |

|     |                                                                   |       |

|     |                                                                   | 12.4  |

|     | 13.4.1 Instruction Format                                         |       |

|     | 13.4.2 Instruction Set                                            |       |

|     |                                                                   |       |

|     |                                                                   |       |

|     |                                                                   |       |

|     |                                                                   |       |

|     |                                                                   |       |

|     |                                                                   |       |

|     | 13.9.1 DSPn Control Register (DSPnCTRL) (n=0-1)                   |       |

|     | 13.9.2 DSPn Execution Register (DSPnEXEC) (n=0-1)                 |       |

|     | 13.9.3 DSPn Debug Register (DSPnDBG)                              |       |

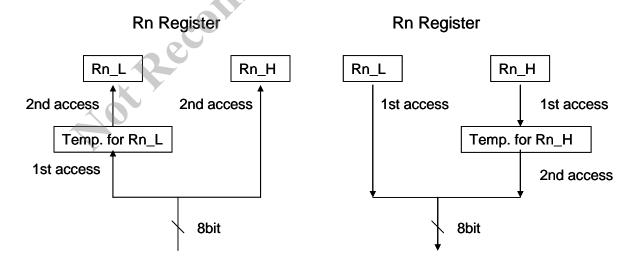

|     | 13.9.4 DSPn Rx LSB Side (DSPn_Rx_L) (n=0-1, x=0-7)                |       |

|     | 13.9.5 DSPn Rx MSB Side (DSPn_Rx_H) (n=0-1,x=0-7)                 |       |

|     | 13.9.6 DSPn Rx LSB Side (DSPn_Rx_L) (n=0-1,x=8-15)                |       |

|     | 13.9.7 DSPn Rx MSB Side (DSPn_Rx_H) (n=0-1,x=8-15)                |       |

|     | 13.9.8 DSPn ACC (DSPn_ACC_x) (n=0-1,x=0-4)                        |       |

|     | 13.9.9 DSPn Program Memory LSB/MSB Side (DSPn_PRG_DATL/H) (n=0-1) |       |

|     | 13.9.10 DSPn Program Memory Address (DSPn_PRG_ADR) (n=0-1)        |       |

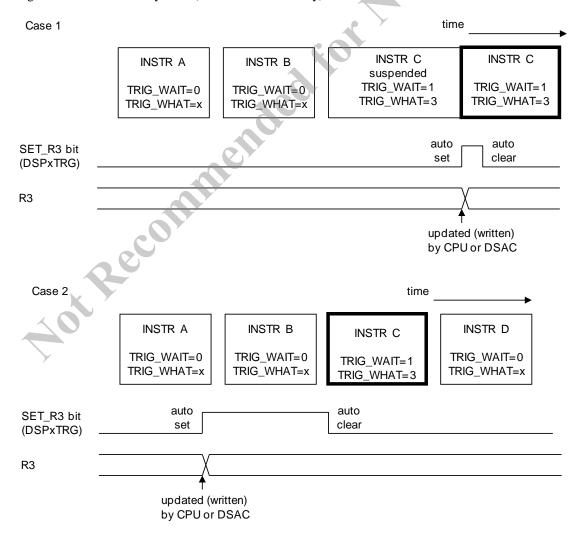

|     | 13.9.11 DSPn Execution Trigger Status (DSPnTRG) (n=0-1)           |       |

|     | 13.9.12 DSPn Access Counter Clear Register (DSPnRST) (n=0-1)      |       |

|     | 13.10 Caution of operation                                        |       |

|     | 13.10.1 Restriction about the TinyDSP interrupt enable bits       | 13-21 |

|     | 13.10.2     | DSP_SS asserted in the DIV instruction    |          | 13-21 |

|-----|-------------|-------------------------------------------|----------|-------|

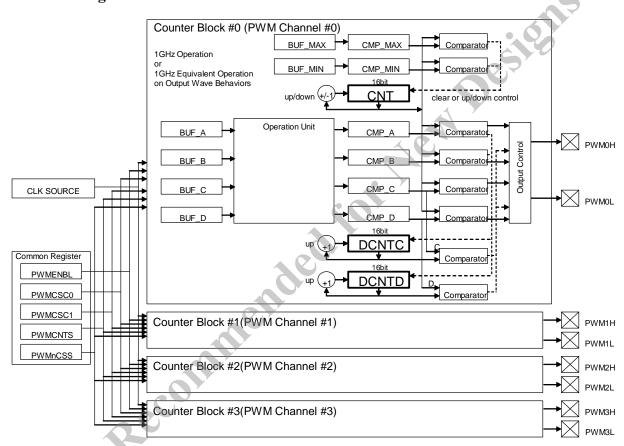

| 14. | High-Resolu | ntion PWM                                 |          | 14-1  |

|     | 14.1 Over   | view                                      |          | 14-1  |

|     | 14.2 Bloc   | k Diagram                                 |          | 14-1  |

|     | 14.3 Reso   | ources                                    |          | 14-2  |

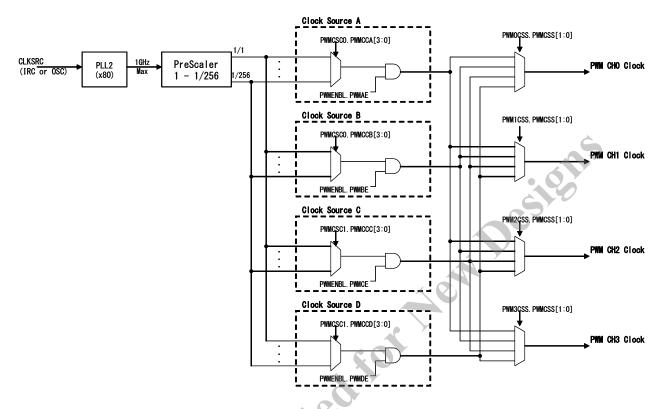

|     |             | k Source selection                        |          |       |

|     |             | ration                                    |          |       |

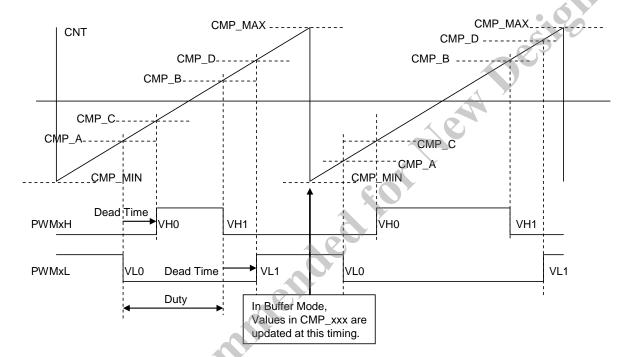

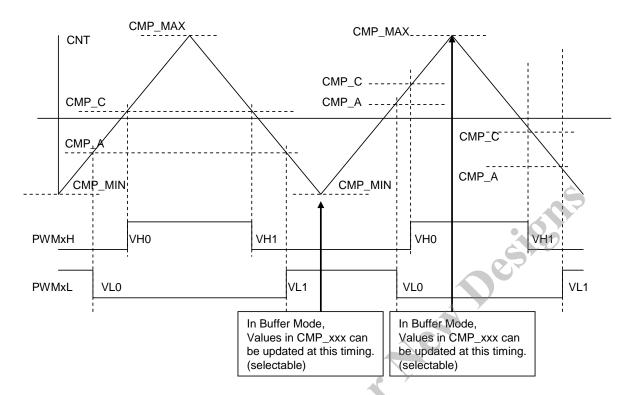

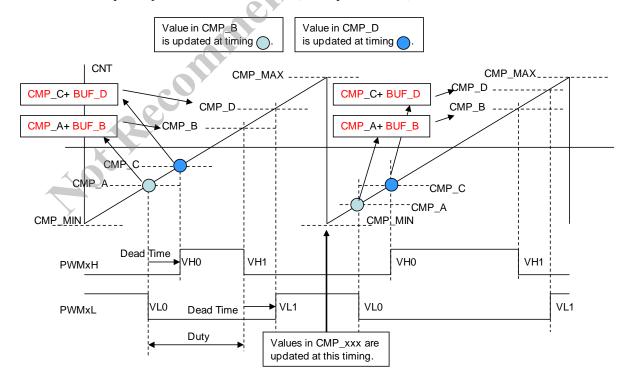

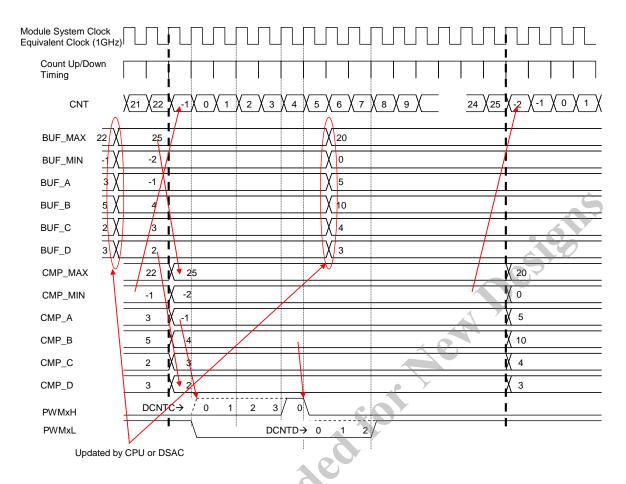

|     | 14.5.1      | Direct Mode and Buffer Mode               |          | 14-8  |

|     |             | PWM Mode 0                                |          | _     |

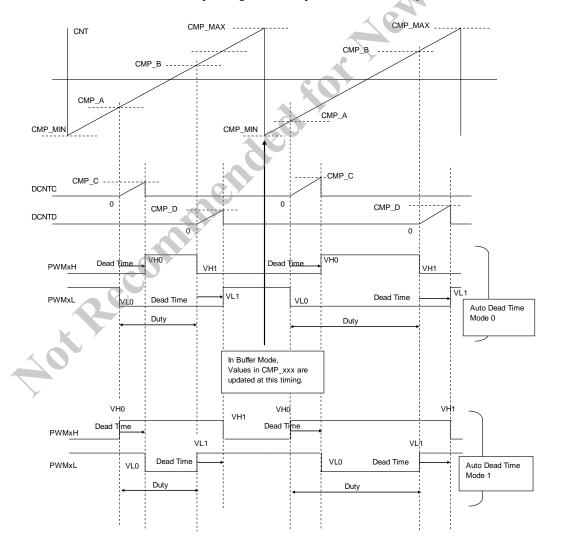

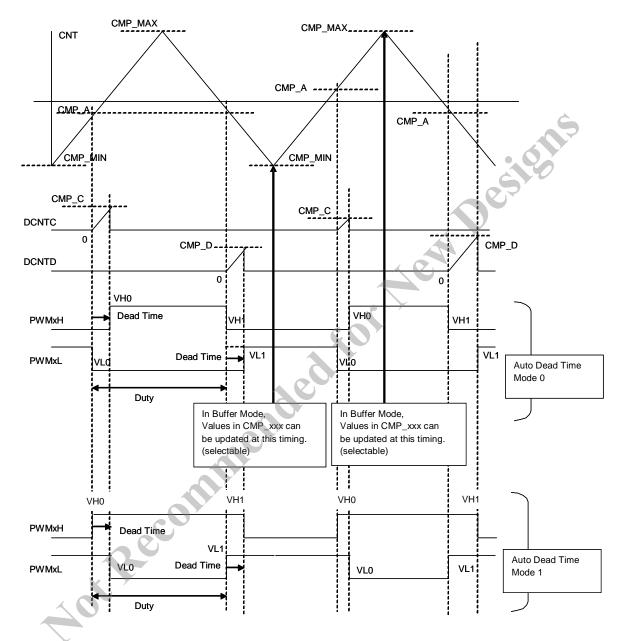

|     |             | PWM Mode 1 (Auto Dead Time)               |          |       |

|     |             | PWM Mode 2 (Phase Shift)                  |          |       |

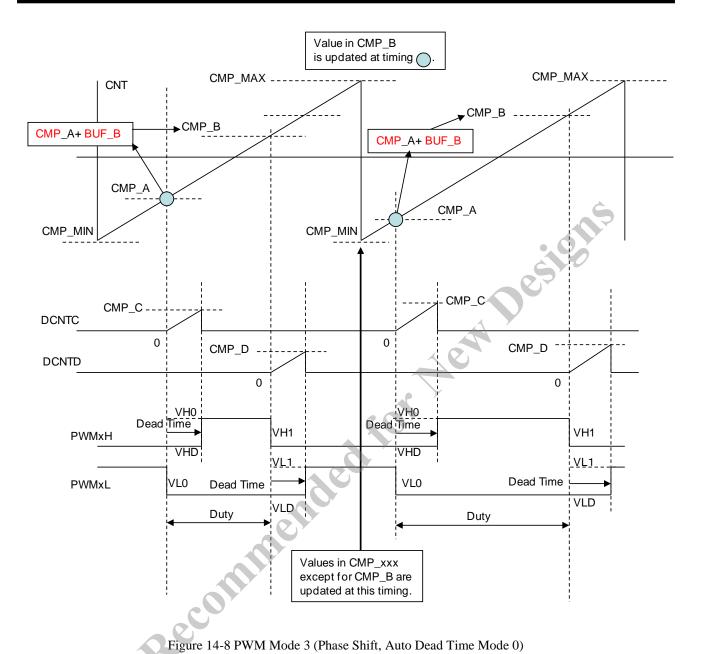

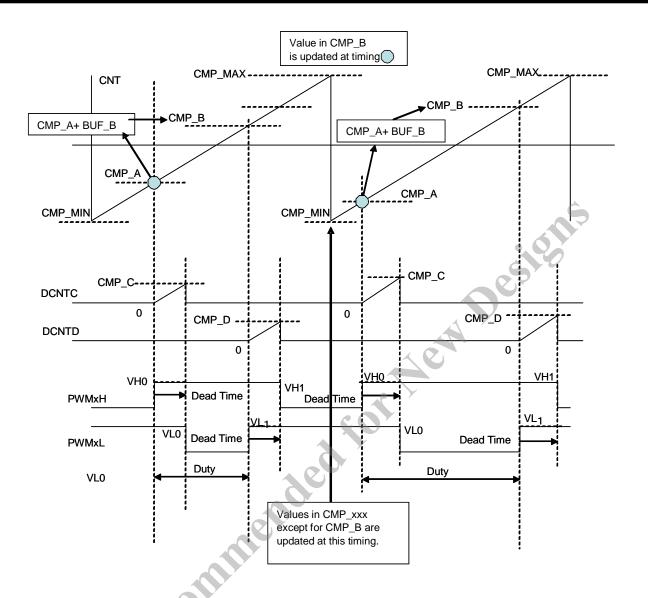

|     |             | PWM Mode 3 (Phase Shift + Auto Dead Time) |          |       |

|     |             | entions or Output Control Conditions      |          |       |

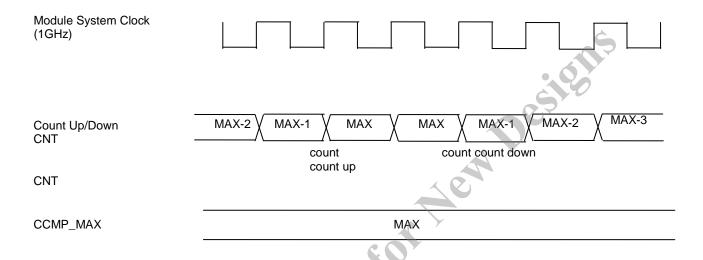

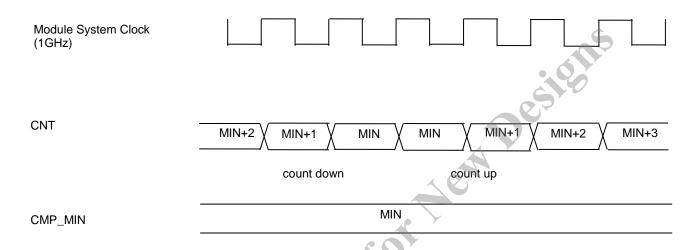

|     |             | ration Timing                             |          |       |

|     |             | rigger Operations                         |          |       |

|     |             | Events for re-trigger                     |          |       |

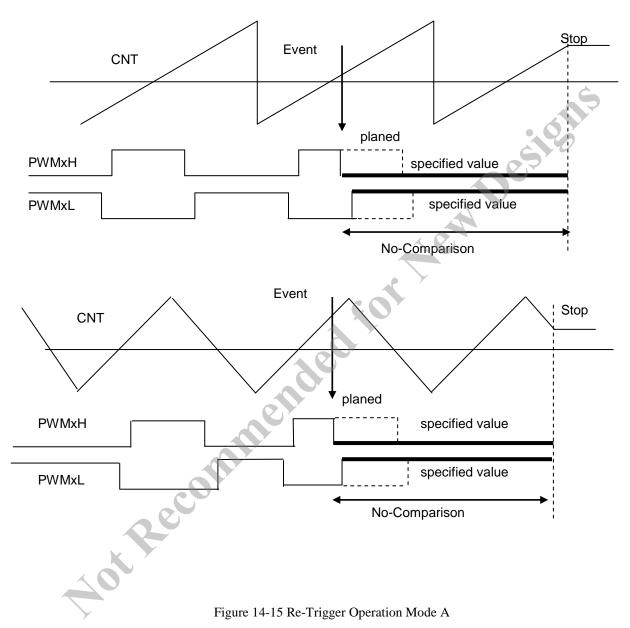

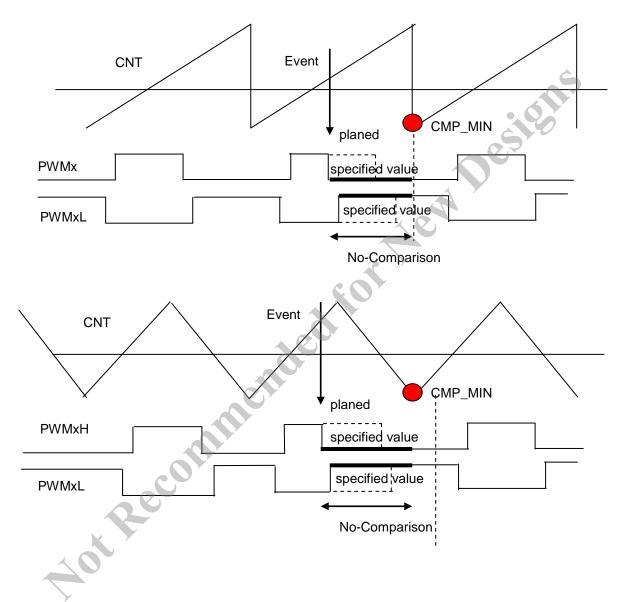

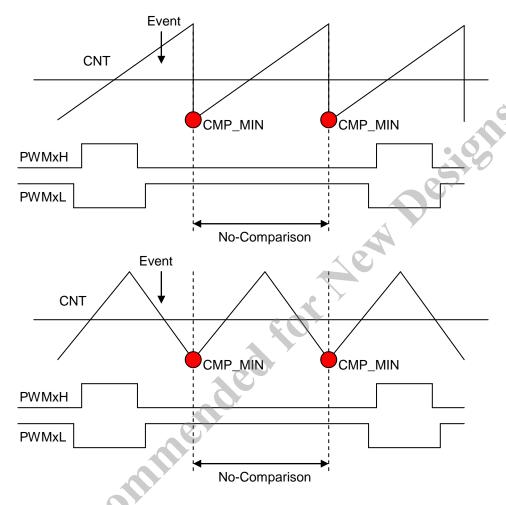

|     | 14.8.2      | Re-Trigger Operation Mode A               |          | 14-26 |

|     | 14.8.3      | Re-Trigger Operation Mode B               | <u>V</u> | 14-27 |

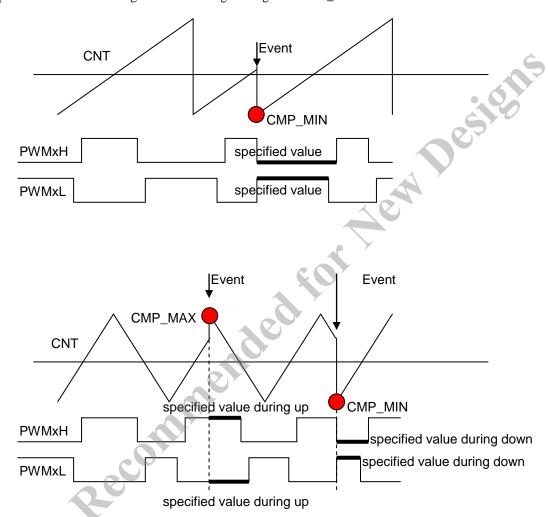

|     | 14.8.4      | Re-Trigger Operation Mode C               |          | 14-28 |

|     | 14.8.5      | Re-Trigger Operation D                    |          | 14-29 |

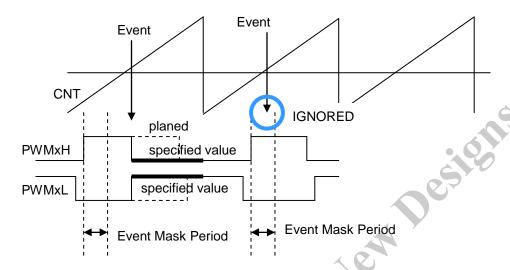

|     | 14.8.6      | Re-Trigger Mask Operation                 |          | 14-30 |

|     | 14.8.7      | 86                                        |          |       |

|     | 14.9 Ever   | at Output                                 |          | 14-31 |

|     | 14.10 Inter | rupt Output                               |          | 14-31 |

|     |             | ster Access                               |          |       |

|     | 14.12 Regi  | ster Description                          |          | 14-33 |

|     |             | PWMENBL                                   |          |       |

|     |             | PWMCSC0                                   |          |       |

|     |             | PWMCSC1                                   |          |       |

|     |             | PWMCNTS                                   |          |       |

|     |             | 6 PWMnCSS (n=0~3)                         |          |       |

|     |             | 5 PWMnEVO0/1/T (n=0~3)                    |          |       |

|     |             | PWMnINTS0/1(n=0~3)                        |          |       |

|     |             | PWMnINTF(n=0~3)                           |          |       |

|     |             | PWMnACCLR (n=0~3)                         |          |       |

|     | 14.12.1     | ,                                         |          |       |

|     |             | 1CNTn(n=0~3)                              |          |       |

|     | 14.12.1     | ,                                         |          |       |

|     | 14.12.1     | ` '                                       |          |       |

|     | 14.12.1     |                                           |          |       |

|     | 14.12.1     | ` '                                       |          |       |

|     | 14.12.1     | ` '                                       |          |       |

|     | 14.12.1     | , ,                                       |          |       |

|     | 14.12.1     | ` '                                       |          |       |

|     | 14.12.1     | ` '                                       |          |       |

|     | 14.12.2     |                                           |          |       |

|     | 14.12.2     | 21 PWMnRTGC (n=0~3)                       |          | 14-52 |

|     | 14.12.22                  | 2 PWMnRTL (n=0~3)                                     | 14-53        |

|-----|---------------------------|-------------------------------------------------------|--------------|

|     | 14.12.2                   | 3 PWMnRTMC (n=0~3)                                    | 14-54        |

|     | 14.12.24                  | 4 PWMnRTMP (n=0~3)                                    | 14-54        |

|     | 14.12.2                   | 5 BUF_MIN/MAXn(n=0~3)                                 | 14-55        |

|     | 14.12.20                  | 6 BUF_A/B/C/Dn (n=0~3)                                | 14-56        |

|     | 14.13 Cauti               | on of Operation                                       | 14-58        |

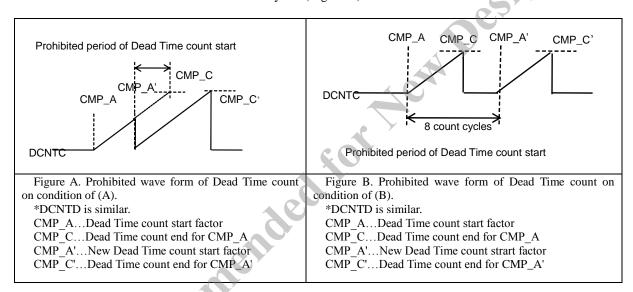

|     | 14.13.1                   | Restrictions about Auto Dead Time Mode of PWM         | 14-58        |

|     | 14.13.2                   | Restriction about PWM Mode 2/3 (Phase Shift Mode)     | 14-59        |

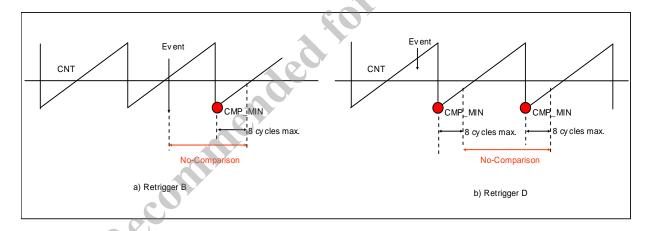

|     | 14.13.3                   | Restriction about PWM Re-Trigger Mode                 | 14-60        |

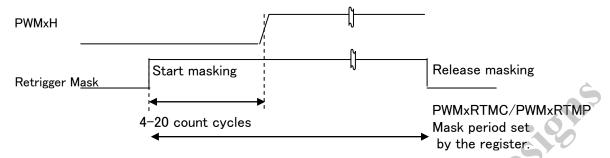

|     | 14.13.4                   | Restriction about PWM Re-Trigger Mask                 | 14-61        |

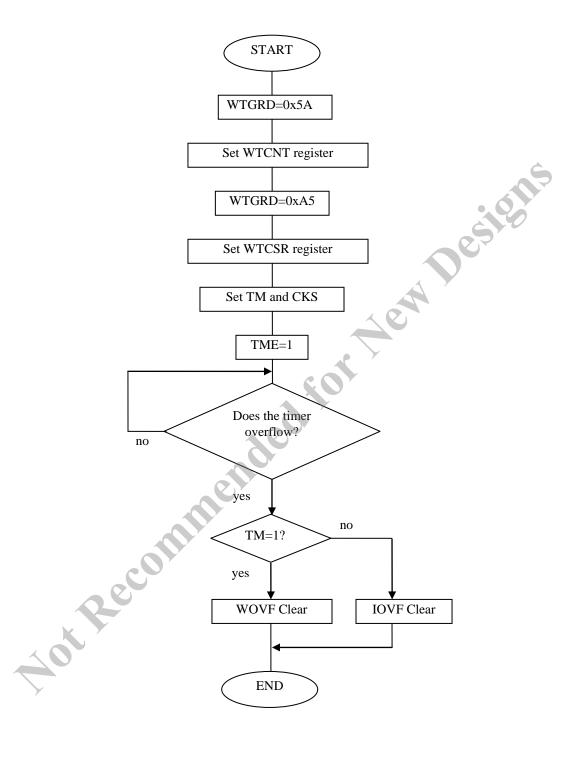

| 15  | Watch Dog T               | Fimer                                                 | 15.1         |

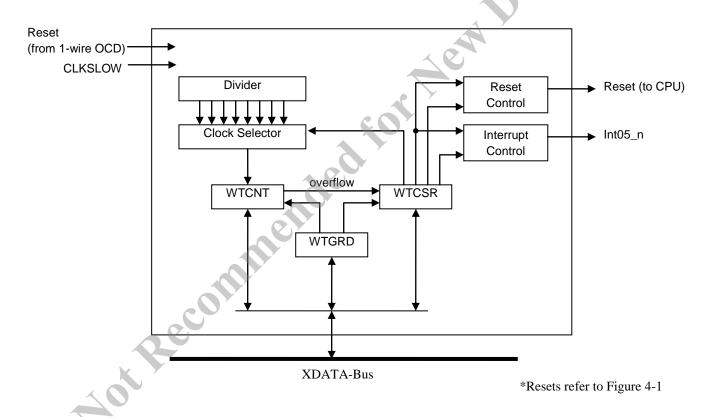

| 15. | _                         | view                                                  |              |

|     |                           | ster Description                                      |              |

|     |                           | WDT Control register                                  |              |

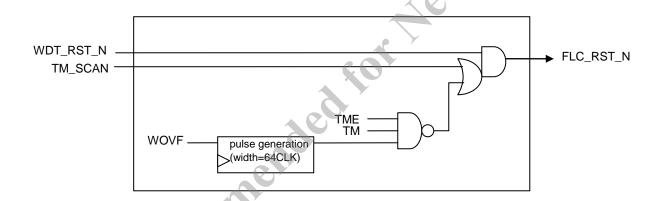

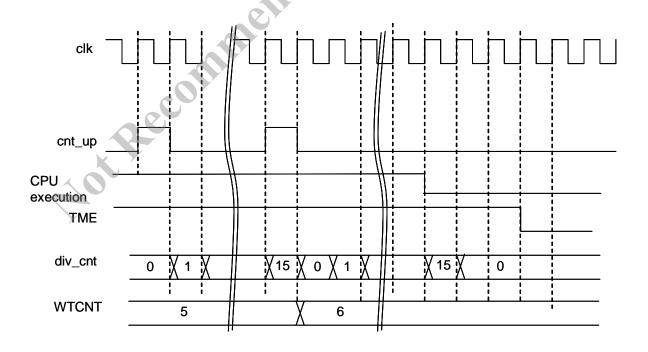

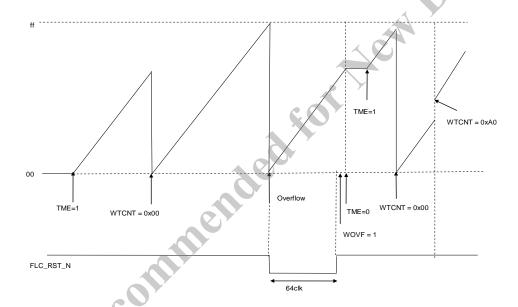

|     | 15.3 Reset                | diagram                                               | 15-3         |

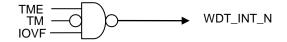

|     |                           | rupt diagram                                          |              |

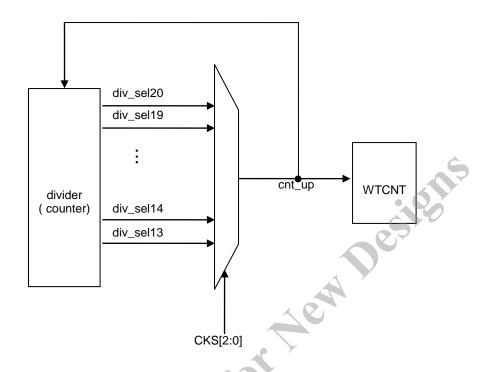

|     |                           | aler                                                  |              |

|     |                           | ation                                                 |              |

|     | 15.6.1                    | How to write into WTCNT and WTCSR                     | 15-5         |

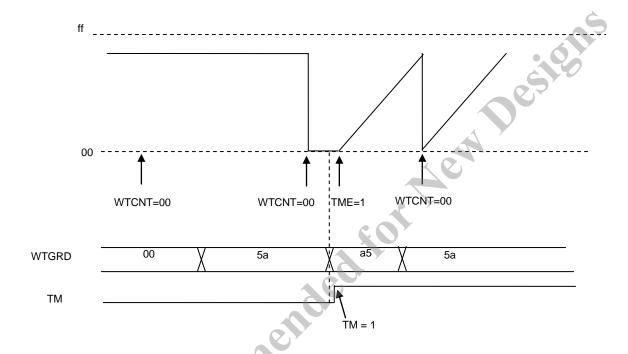

|     | 15.6.2                    | How to write into WTCNT and WTCSRWatch dog timer mode | 15-6         |

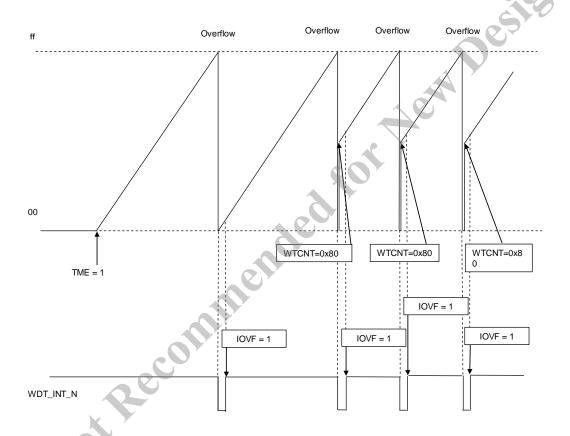

|     | 15.6.3                    | Interval Timer Mode                                   | 15-7         |

| 1.0 | 1 C 1 '4 T'               | (TMR)                                                 | 16.1         |

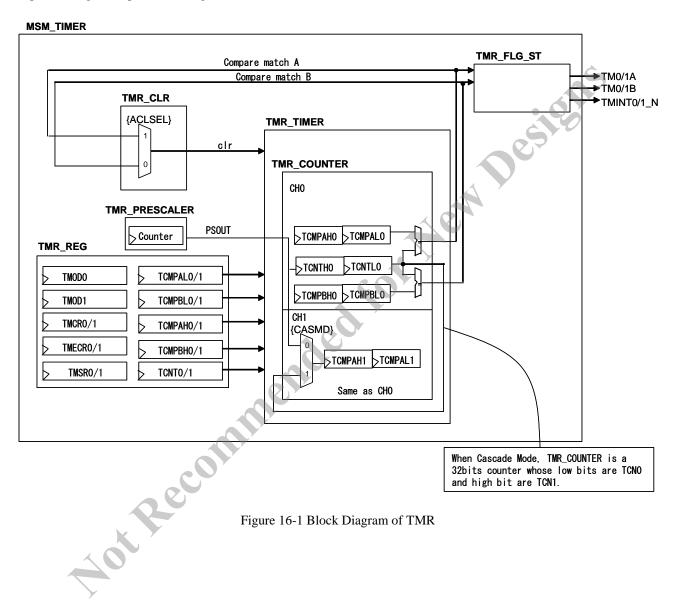

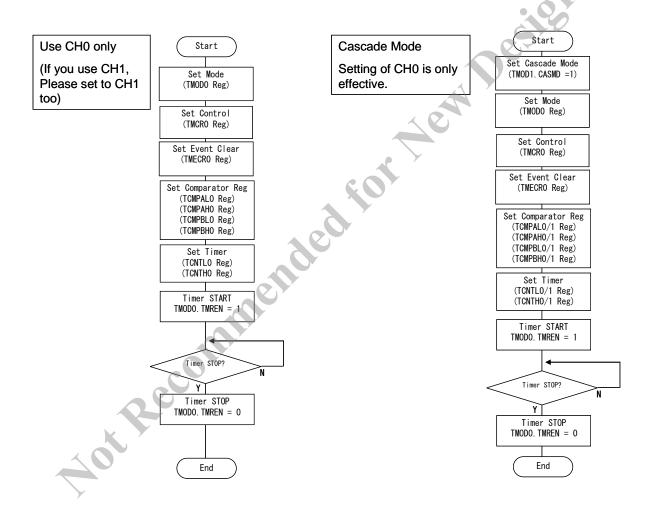

| 16. | 16 bit Timer<br>16.1 Over | view                                                  | 16.1         |

|     | 16.1 Over                 | ster Description                                      | 16-2         |

|     | 16.2.1                    | _                                                     |              |

|     | 16.2.1                    | Timer control Mode Register (TMOD1)                   |              |

|     | 16.2.3                    | Timer n Status Register (TMSRn) (n=0-1)               |              |

|     | 16.2.4                    | Timer n Control register (TMCRn) (n=0-1)              |              |

|     | 16.2.5                    | Timer n event clear register (TMECRn) (n=0-1)         |              |

|     | 16.2.6                    | Timer n compare match A-L (TCMPALn) (n=0-1)           |              |

|     | 16.2.7                    | Timer n compare match A-H (TCMPAHn) (n=0-1)           |              |

|     | 16.2.8                    | Timer n compare match B-L (TCMPBLn) (n=0-1)           |              |

|     |                           | Timer n compare match B-H (TCMPBHn) (n=0-1)           |              |

|     |                           | Timer n counter L (TCNTLn) (n=0-1)                    |              |

|     |                           | Timer n counter H (TCNTHn) (n=0-1)                    |              |

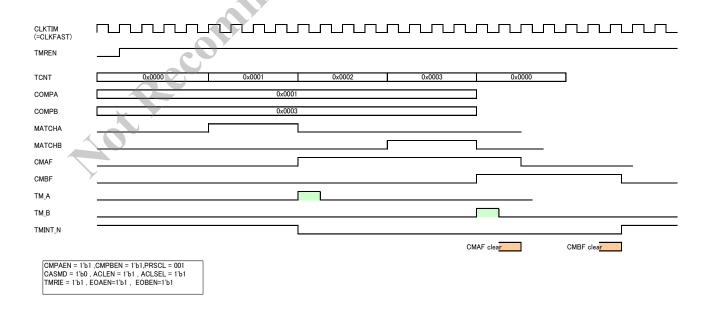

|     |                           | ation                                                 |              |

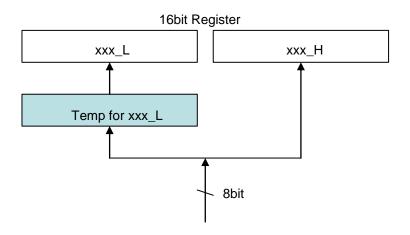

|     | 16.3.1                    | 16 bit Register access                                |              |

|     | 16.3.2                    | Counter Operation                                     |              |

|     | 16.3.3                    | Compare match operation                               |              |

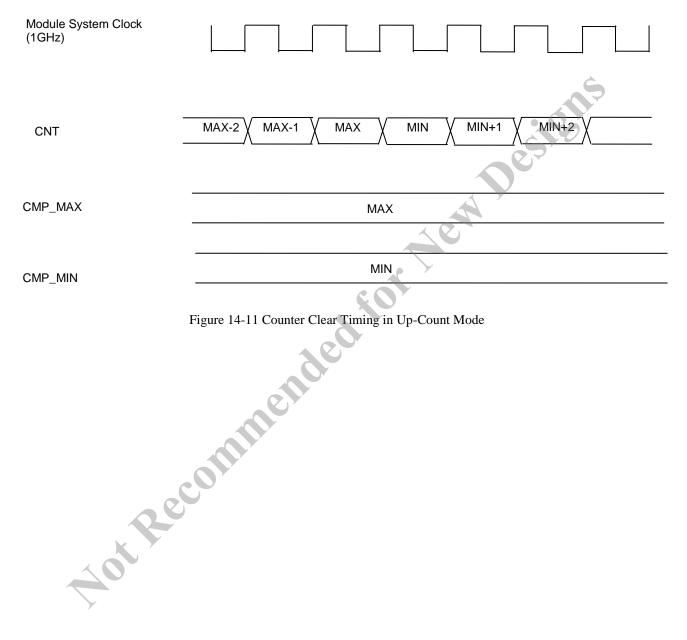

|     | 16.3.4                    | Auto Clear                                            |              |

|     | 16.3.5                    | PWM Event Clear                                       |              |

|     | 16.3.6                    | 32bit Counter Mode                                    |              |

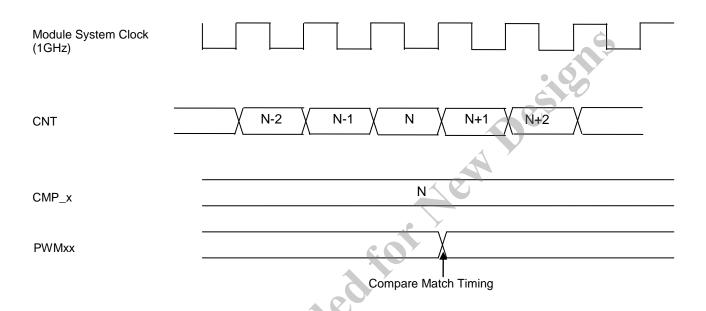

|     | 16.3.7                    | Compare match timing                                  |              |

| 1.7 |                           | 1                                                     | 10 10        |

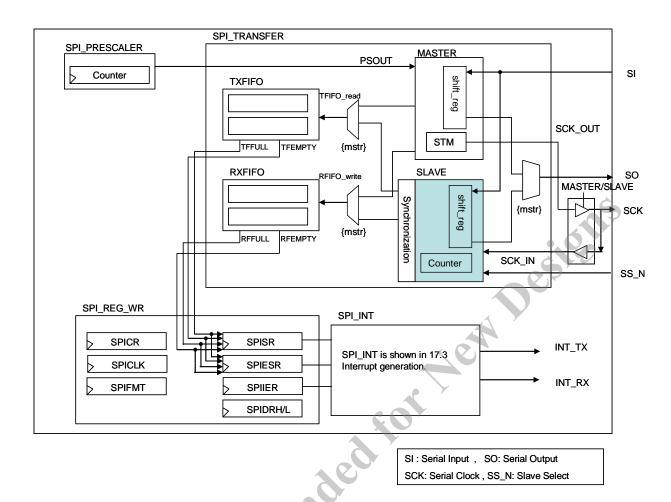

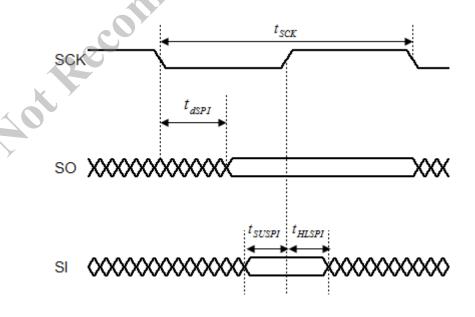

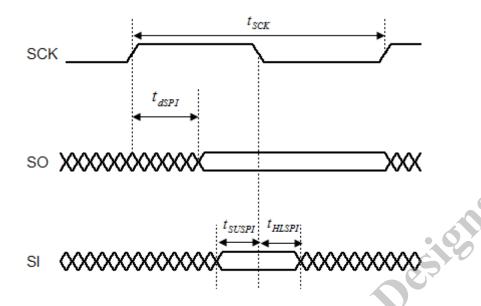

| 17. | SPI 17-1<br>17.1 Over     | view                                                  | 17 1         |

|     |                           | view                                                  | 1/-1<br>17-2 |

|     |                           |                                                       |              |

|     | 17.2.1             | SPI Control Register (SPICR)                                   | 17-3  |

|-----|--------------------|----------------------------------------------------------------|-------|

|     | 17.2.2             | SPI CLOCK DIV Register (SPICLK)                                | 17-5  |

|     | 17.2.3             | SPI data format Register (SPIFMT)                              |       |

|     | 17.2.4             |                                                                |       |

|     | 17.2.5             | SPI Error Status register (SPIESR)                             |       |

|     | 17.2.6             | ,                                                              |       |

|     | 17.2.7             |                                                                |       |

|     | 17.2.8             |                                                                |       |

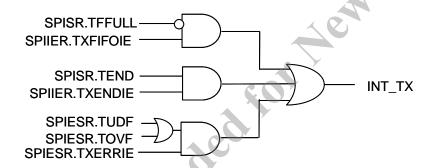

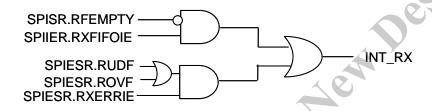

|     |                    | rrupt generation                                               |       |

|     | 17.3.1             | INT TX                                                         |       |

|     |                    | INT RX                                                         |       |

|     |                    |                                                                |       |

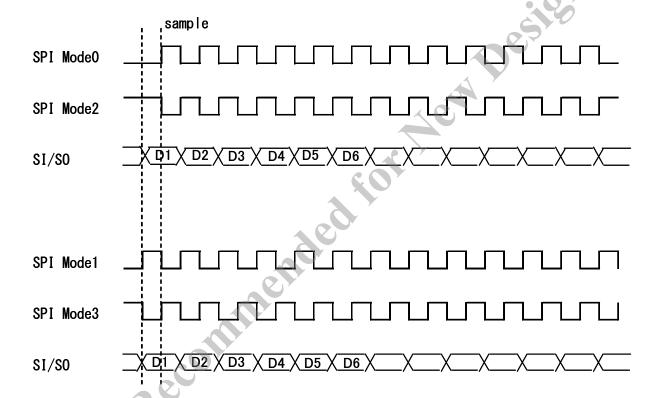

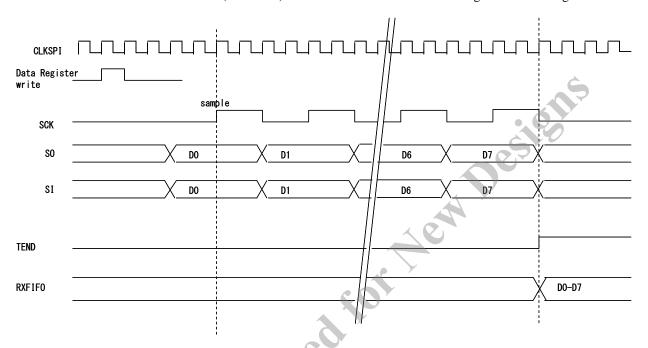

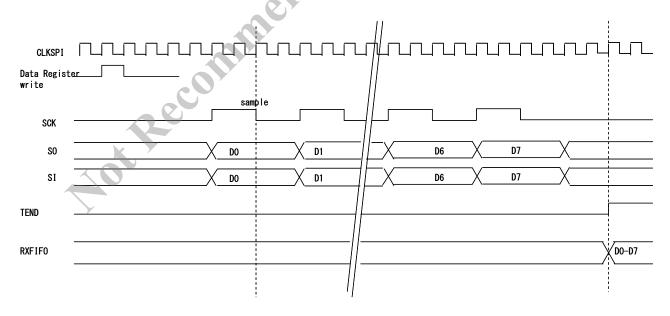

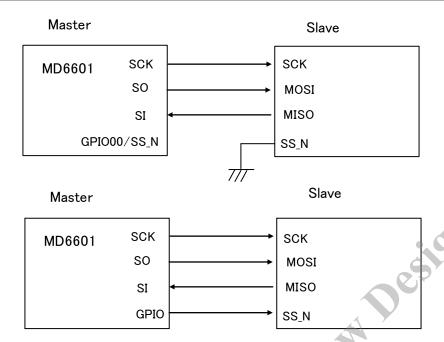

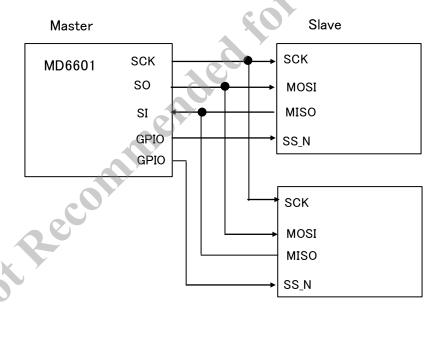

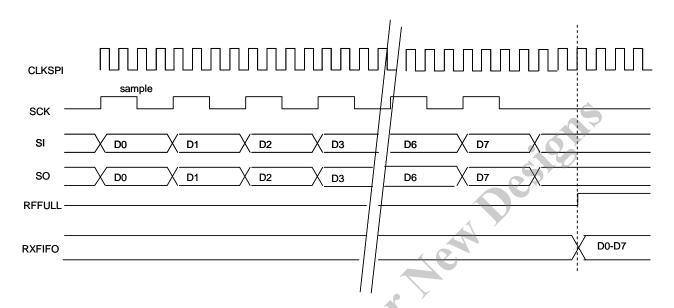

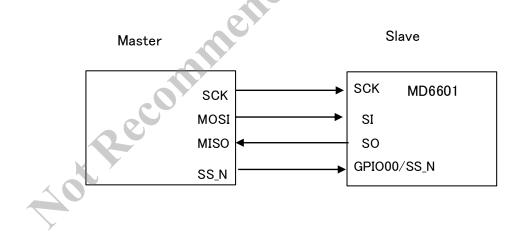

|     | 17.4 1111          | ing chart and Connection  Master mode Slave Moderation         | 17 11 |

|     | 17.4.1             | Slave Mode                                                     | 17 13 |

|     | 17.4.2<br>17.5 Ope | ration                                                         | 17-13 |

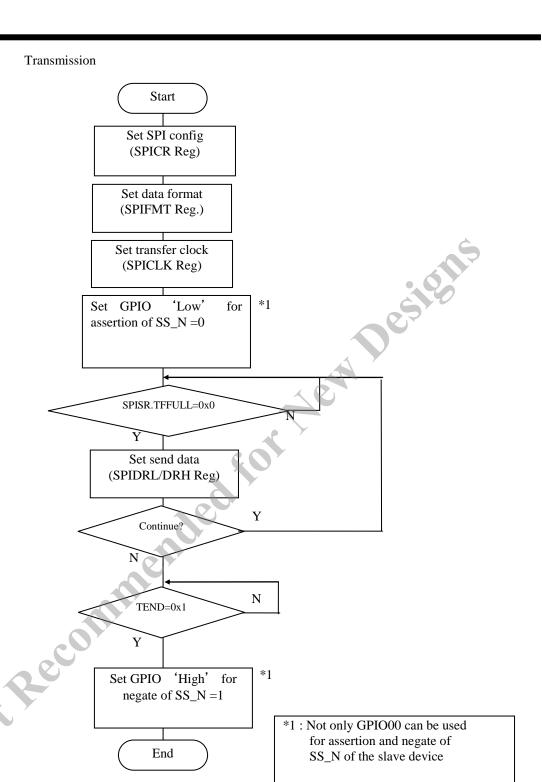

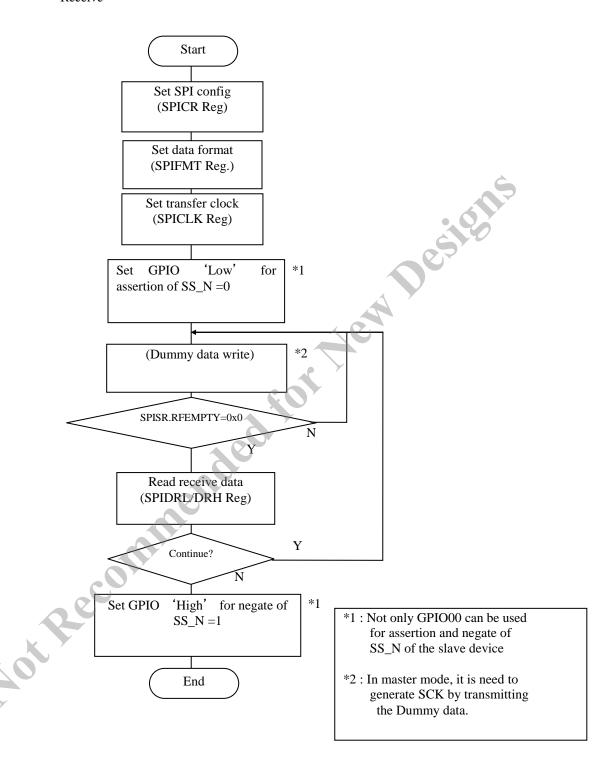

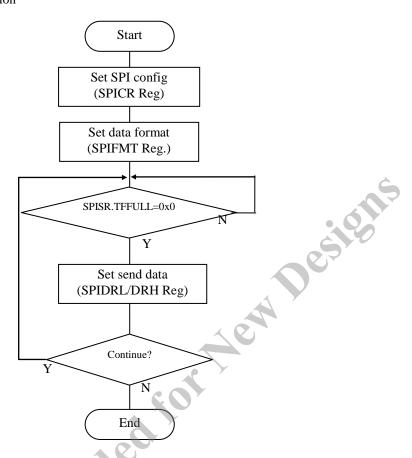

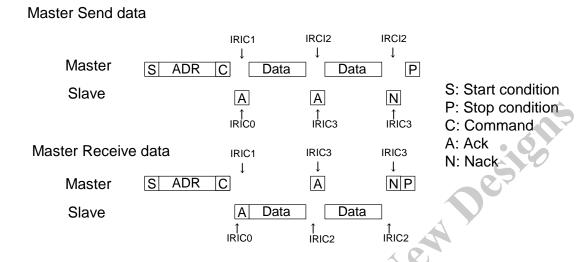

|     | 17.5 Ope           |                                                                |       |

|     |                    |                                                                | 17 17 |

|     | 17.5.2             | Stave Mode                                                     | 1/-1/ |

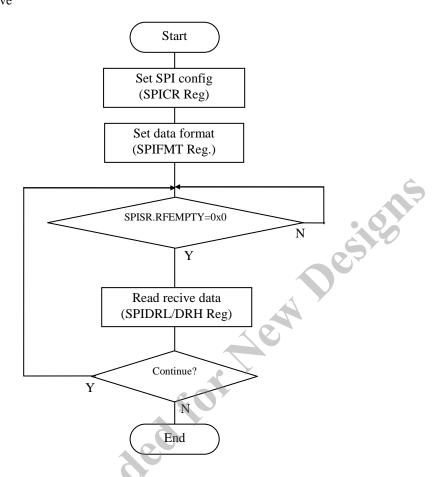

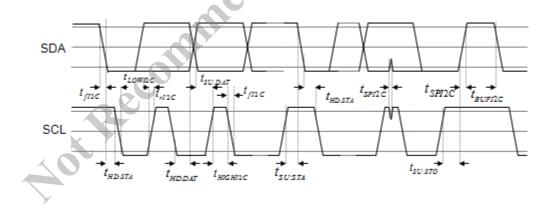

| 18. | I2C (SMBU          | VS)rview                                                       | 18-1  |

|     | 18.1 Ove           | rview                                                          | 18-1  |

|     | 18.2 Reg           | ister Description                                              | 18-2  |

|     | 18.2.1             | I2C Bus Control Register (ICCR) I2C Bus Status Register (ICSR) | 18-3  |

|     | 18.2.2             |                                                                |       |

|     | 18.2.3             | I2C Bus Receive Data Register (ICRXDR)                         | 18-6  |

|     | 18.2.4             | I2C Bus Transmit Data Register (ICTXDR)                        | 18-7  |

|     | 18.2.5             | Transmit Address Register (ICTSAR)                             | 18-7  |

|     | 18.2.6             | Slave Address Register (ICSAR)                                 | 18-8  |

|     | 18.2.7             | Clock Divid Register (ICCLK)                                   | 18-8  |

|     | 18.2.8             | I2C Command Register (ICCMD)                                   | 18-9  |

|     | 18.2.9             | I2C Bus SDA Setup Time Register (ICSSTR)                       | 18-10 |

|     | 18.2.10            | ) I2C Bus SDA Hold Time Register (ICSHTR)                      | 18-11 |

|     |                    | 1 I2C Bus SDA Hardware Status Register 0(ICHDSR0)              |       |

|     | 18.2.12            | 2 I2C Bus SDA Hardware Status Register 1(ICHDSR1)              | 18-12 |

|     |                    | 3 I2C Time Base Register                                       |       |

|     | 18.2.1             | 4 SMBUS INT Status Register                                    | 18-13 |

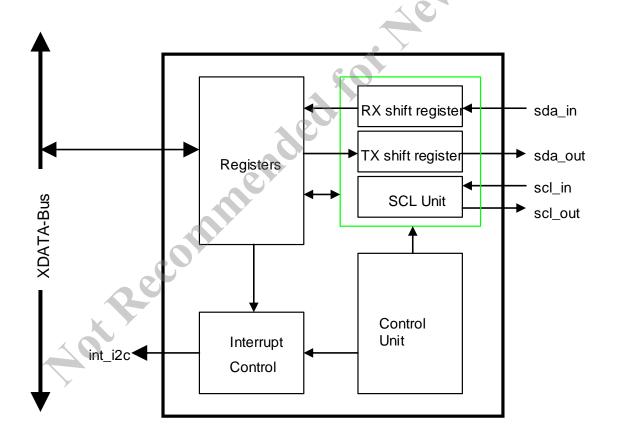

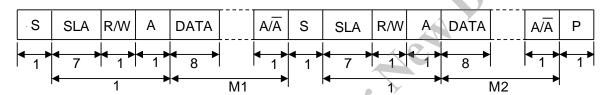

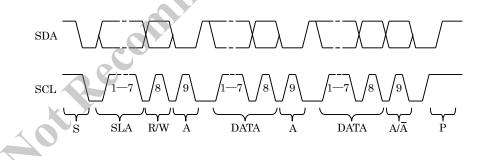

|     | 18.3 I2C           | bus data format                                                | 18-14 |

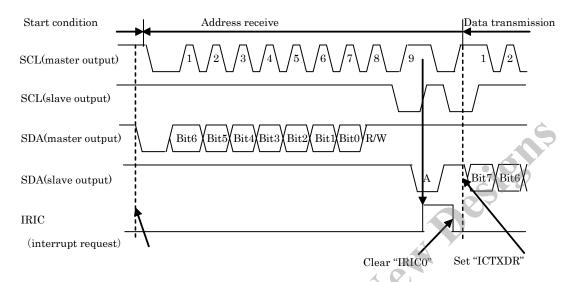

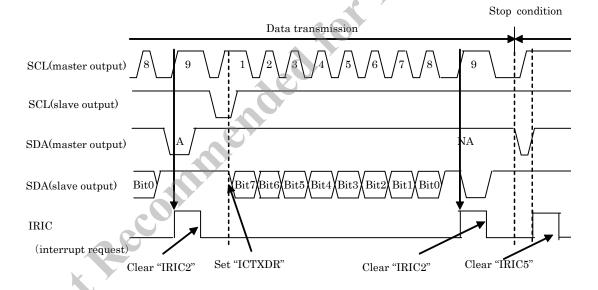

|     | 18.4 Slav          | e receiver operation                                           | 18-15 |

|     |                    | e transmitter operation                                        |       |

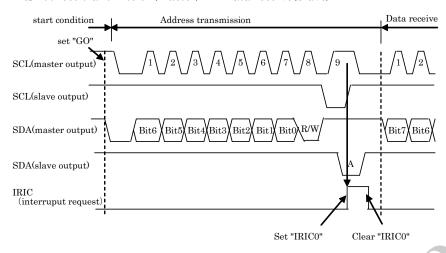

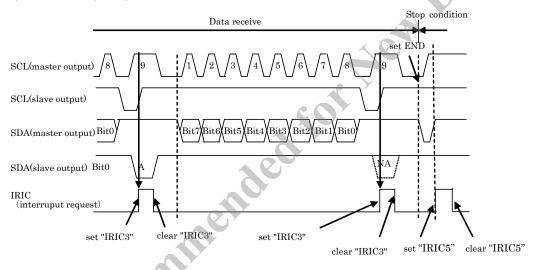

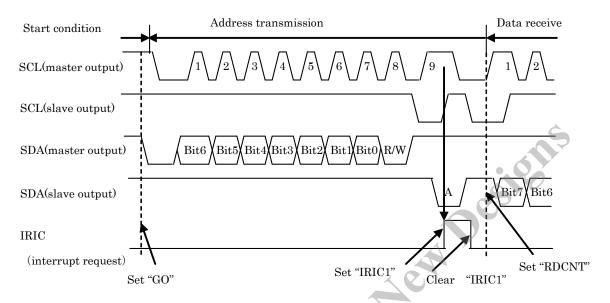

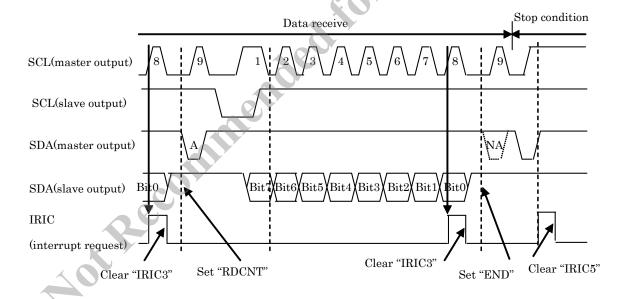

|     |                    | ter receiver operation                                         |       |

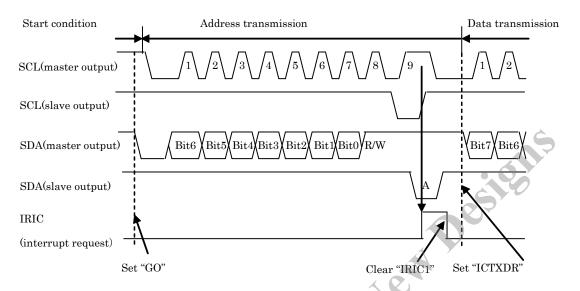

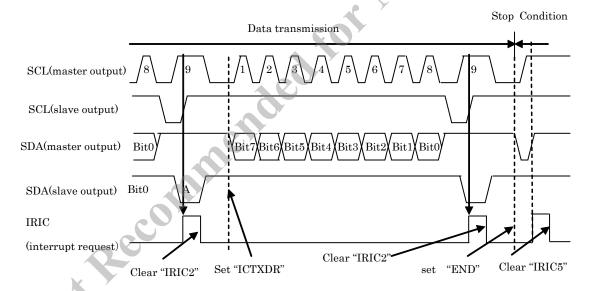

|     |                    | ter transmitter operation                                      |       |

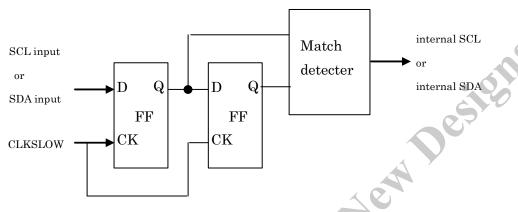

|     |                    | se Filter                                                      |       |

|     |                    |                                                                | 10 23 |

| 19. | UART 19-1          |                                                                |       |

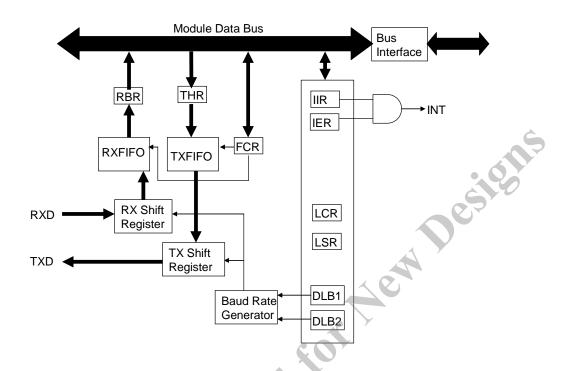

|     |                    | rview                                                          |       |

|     |                    | ernal (off-chip) connections                                   |       |

|     | Ü                  | ister Description                                              |       |

|     | 19.3.1             |                                                                |       |

|     | 19.3.2             | Interrupt Enable Register (IER)                                | 19-3  |

|     | 19.3.3       | Interrupt Identification Register (IIR)         | 19-4  |

|-----|--------------|-------------------------------------------------|-------|

|     | 19.3.4       | FIFO Control Register (FCR)                     | 19-5  |

|     | 19.3.5       | Line Control Register (LCR)                     | 19-6  |

|     | 19.3.6       | Line Status Register (LSR)                      | 19-7  |

|     | 19.3.7       | Divisor Latches                                 | 19-8  |

|     | 19.3.8       | Baud rate                                       | 19-9  |

|     | 19.4 Oper    | ation                                           | 19-10 |

|     | 19.5 Cauti   | on of operation                                 | 19-10 |

|     | 19.5.1       | Restriction about the UART register access      | 19-10 |

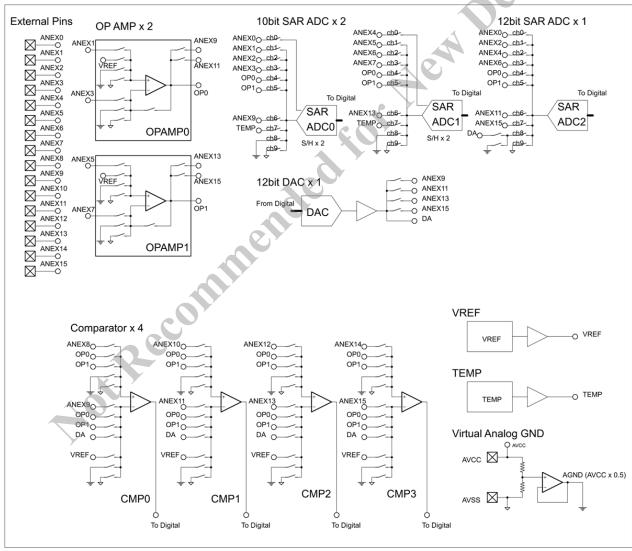

| 20. | Analog Inter | -Connection Network                             | 20-1  |

|     |              | view                                            |       |

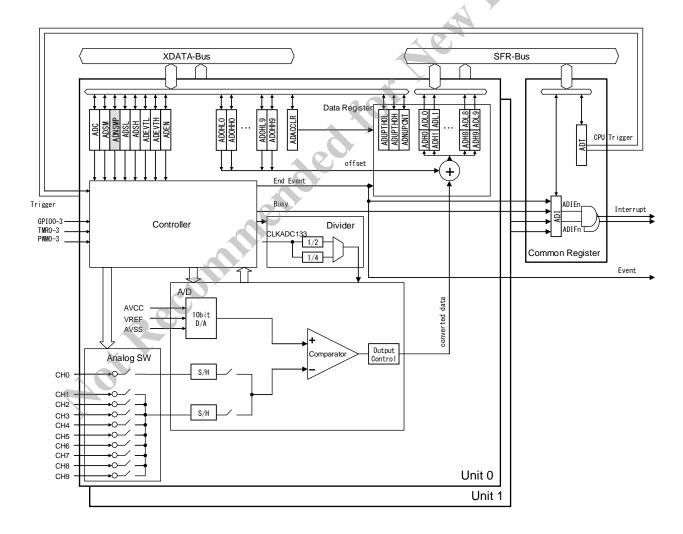

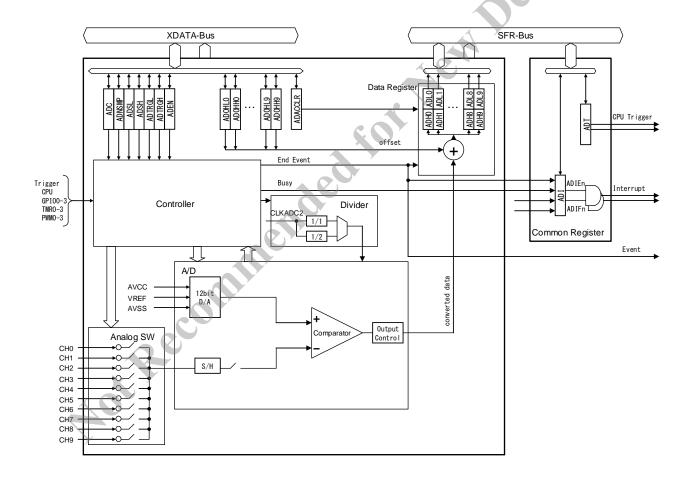

| 21. | High Speed   | 10bit SAR ADC                                   | 21-1  |

|     | 21.1 Over    | view                                            | 21-1  |

|     | 21.2 Regis   | ster Description                                | 21-3  |

|     | 21.2.1       | ADCn (ADC Configuration Register)               | 21-5  |

|     | 21 2 2       | ADSMn (ADC Sample Mode Register)                | 21-6  |

|     | 21.2.3       | ADSI n (ADC Channel Sequence I Register)        | 21.6  |

|     | 21.2.4       | ADSHn (ADC Channel Sequence H Register)         | 21-7  |

|     | 21.2.5       | ADTRGLn (ADC Event Source L Register)           | 21-8  |

|     | 21.2.6       | ADTRGHn (ADC Event Source H Register)           |       |

|     | 21.2.7       | ADENn (ADC Enable Register)                     |       |

|     | 21.2.8       | ADACCLRn (ADC Access Counter Clear Register)    |       |

|     | 21.2.9       | ADUPTHL0n (ADC Ch0 Update Threshold L Register) | 21-10 |

|     | 21.2.10      | ADUPTHH0n (ADC Ch0 Update Threshold H Register) | 21-10 |

|     | 21.2.11      | ADNUPCNTn (ADC Ch0 Non-update Count Register)   | 21-11 |

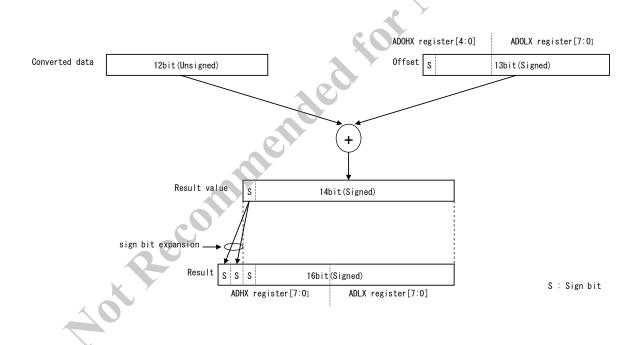

|     | 21.2.12      | ADOLXn (ADC ChX Offset Data L Register, n=0-1)  | 21-12 |

|     | 21.2.13      | ADOHXn (ADC ChX Offset Data H Register, n=0-1)  | 21-13 |

|     | 21.2.14      | ADLXn (ADC ChX Data L Register, n=0-1)          | 21-14 |

|     | 21.2.15      | ADHXn (ADC ChX Data H Register, n=0-1)          | 21-15 |

|     | 21.2.16      | ADT (ADC Trigger Register)                      | 21-16 |

|     | 21.2.17      | ADI (ADC Interrupt Register)                    | 21-17 |

|     | 21.3 Oper    | ation                                           | 21-18 |

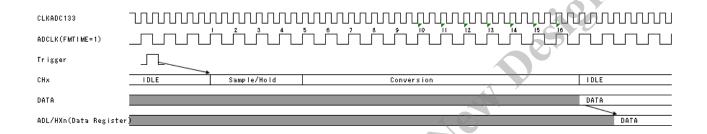

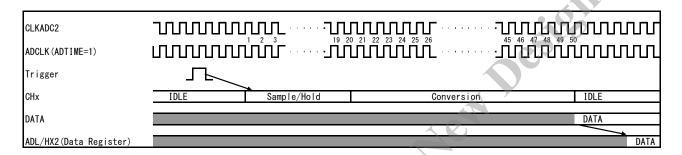

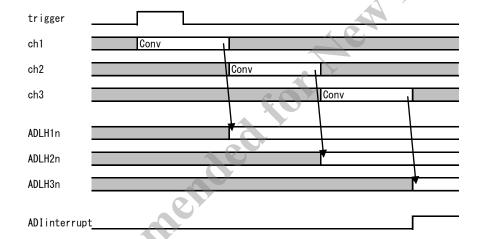

|     | 21.3.1       | Basic operation                                 | 21-18 |

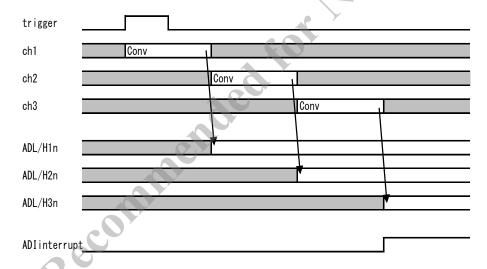

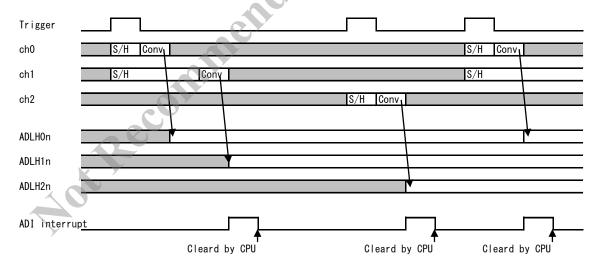

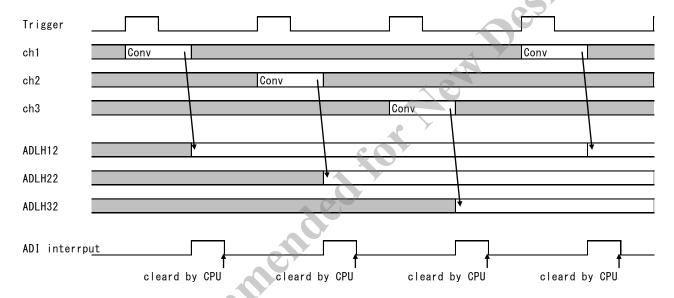

|     | 21.3.2       | Conversion Mode                                 | 21-19 |

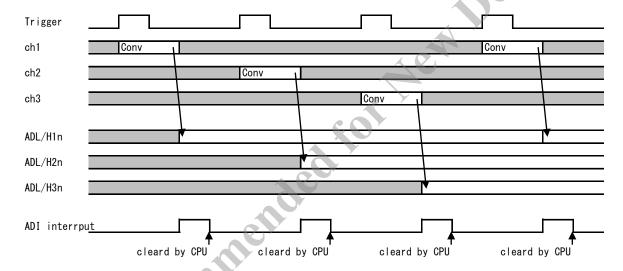

|     |              | .3.2.1. "Burst until Sequence End" mode         |       |

|     | 21           | .3.2.2. "Step and Round Sequence" Mode          |       |

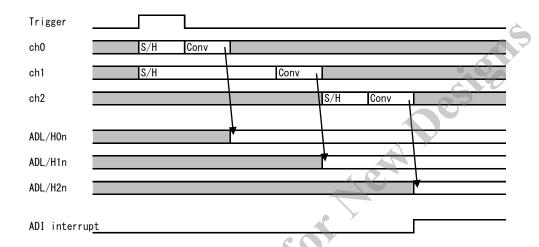

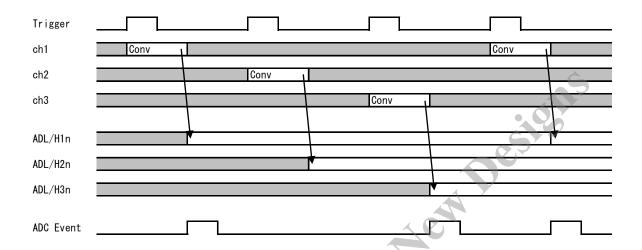

|     | 21.3.3       | Dual Sample/Hold                                |       |

|     | 21.3.4       | Conversion start trigger                        |       |

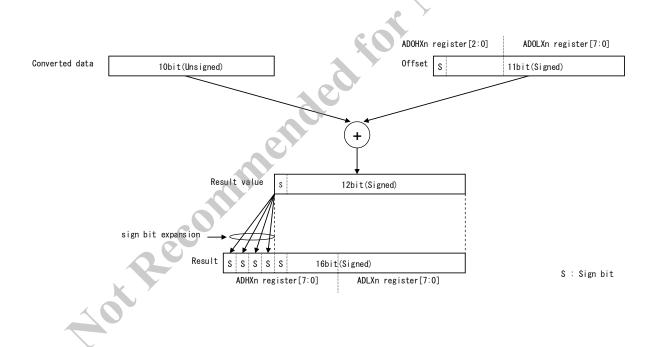

|     | 21.3.5       | Converted data offset adjustment                |       |

|     | 21.3.6       | Interrupts                                      |       |

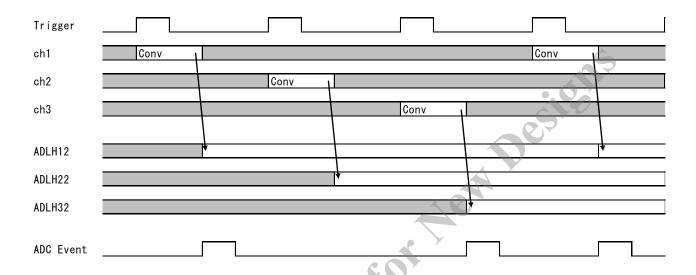

|     | 21.3.7       | ADC Event                                       |       |

|     | 21.3.8       | Reading converted data                          |       |

|     | 21.3.9       | Threshold for conversion data update            |       |

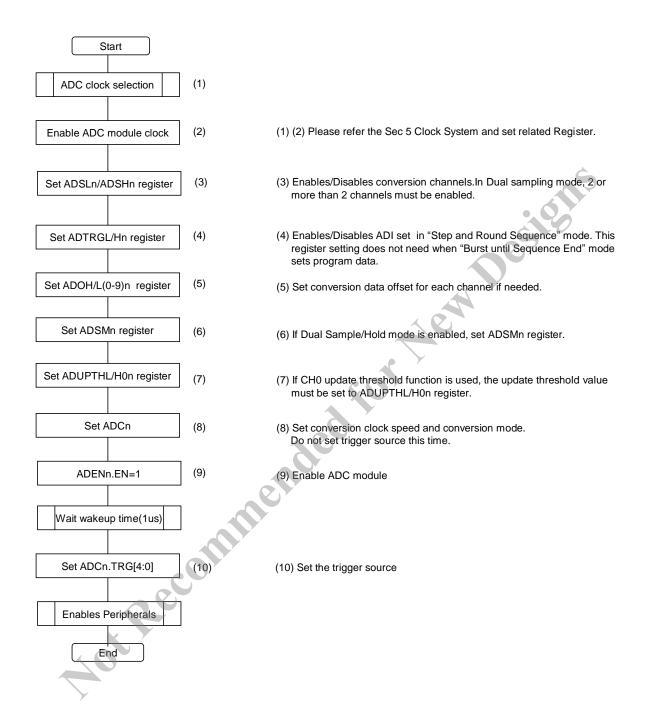

|     |              | Initialization sequence                         |       |

|     |              | tation of ADC10                                 |       |

|     | 21.4.1       | Disabling ADC                                   | 21-25 |

|     | 21.4.2       | Going to standby mode                                    | 21-25 |

|-----|--------------|----------------------------------------------------------|-------|

|     |              | Clock frequency setting                                  |       |

| 22  |              | on 12 bit SAR ADC                                        |       |

| 22. | -            | view                                                     |       |

|     |              | ster Description                                         |       |

|     | _            | ADC2 (ADC Configuration Register)                        |       |

|     |              | ADSL2 (ADC Channel Sequence L Register)                  |       |

|     |              | ADSH2 (ADC Channel Sequence H Register)                  |       |

|     |              | ADTRGL2 (ADC Event Source L Register)                    |       |

|     |              | ADTRGH2 (ADC Event Source H Register)                    |       |

|     |              | ADEN2 (ADC Enable Register)                              |       |

|     |              | ADACCLR2 (ADC Access Counter Clear Register)             |       |

|     | 22.2.8       | ADUPTHL02 (ADC Ch0 Update Threshold L Register)          | 22-9  |

|     | 22.2.9       | ADUPTHH02 (ADC Ch0 Update Threshold H Register)          | 22-9  |

|     |              | ADNUPCNT2 (ADC Ch0 Non-update Count Register)            |       |

|     |              | ADOLX2 (ADC ChX Offset Data L Register)                  |       |

|     |              | ADOHX2 (ADC ChX Offset Data H Register, X=0-9)           |       |

|     | 22.2.13      | ADLX2 (ADC ChX Data L Register)                          | 22-12 |

|     | 22.2.14      | ADUV2 (ADC Chy Data II Pagister)                         | 22 13 |

|     | 22 2 15      | ADT (ADC Trigger Pegister)                               | 22 13 |

|     | 22.2.16      | ADI (ADC Ingger Register)                                | 22-13 |

|     | 22.3 Oper    | ution                                                    | 22 11 |

|     | 22.3.1       | Basic operation                                          | 22-14 |

|     | 22.3.2       | Conversion Mode                                          | 22-15 |

|     | 22           | .3.2.1. Burst until Sequence End mode                    | 22-15 |

|     | 22           | .3.2.2. Step and Round Sequence Mode                     | 22-16 |

|     | 22.3.3       | Conversion start trigger                                 | 22-17 |

|     | 22.3.4       | Converted data offset adjustment                         | 22-17 |

|     | 22.3.5       | Interrupts                                               | 22-18 |

|     | 22.3.6       | ADC Event                                                | 22-18 |

|     | 22.3.7       | Reading converted data                                   | 22-18 |

|     | 22.3.8       | Threshold for conversion data update                     | 22-18 |

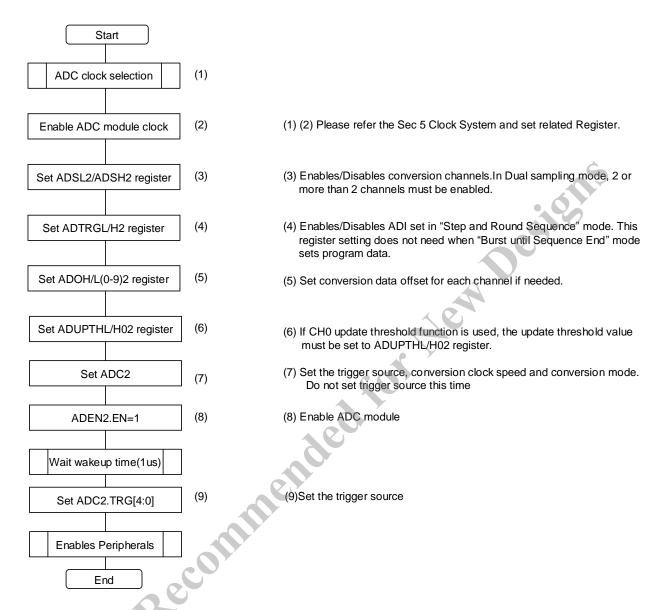

|     | 22.3.9       | Initialization sequence                                  | 22-19 |

|     | 22.4 Limi    | tation of ADC12                                          | 22-20 |

|     | 22.4.1       | Disabling ADC                                            | 22-20 |

|     | 22.4.2       | Going to standby mode                                    | 22-20 |

|     | 22.5 Cauti   | ion of operation                                         | 22-20 |

|     | 22.5.1       | Restriction about the conversion time of the 12 bits ADC | 22-20 |

| 23. | High Precisi | on 12 bit DAC                                            | 23-1  |

| -0. | U            | view                                                     |       |

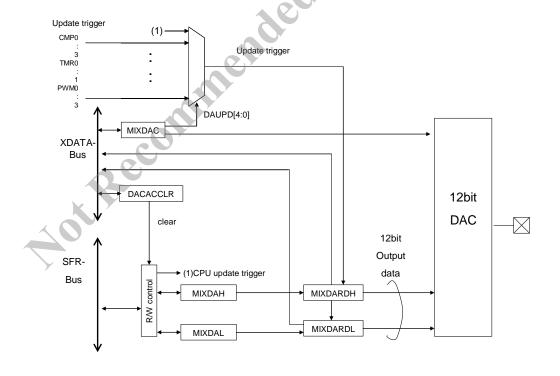

|     | 23.2 Block   | k Diagram                                                | 23-1  |

|     | 23.3 Regis   | ster Description                                         | 23-2  |

|     | 23.3.1       | Mix DAC Configuration (MIXDAC)                           |       |

|     | 23.3.2       | Mix DAC Data L (MIXDAL)                                  |       |

|     | 23.3.3       | Mix DAC Data H (MIXDAH)                                  | 23-3  |

|     | 23.3.4       | Mix DAC Read Data L (MIXDARDL)                           | 23-3  |

|     | 23.3.5        | Mix DAC Read Data H (MIXDARDH)                                               | 23-4         |

|-----|---------------|------------------------------------------------------------------------------|--------------|

|     | 23.3.6        | Mix DAC Access Counter Clear Register (DACACCLR)                             | 23-4         |

|     | 23.3.7        | Mix DAC Output select Register (DACOUT)                                      | 23-5         |

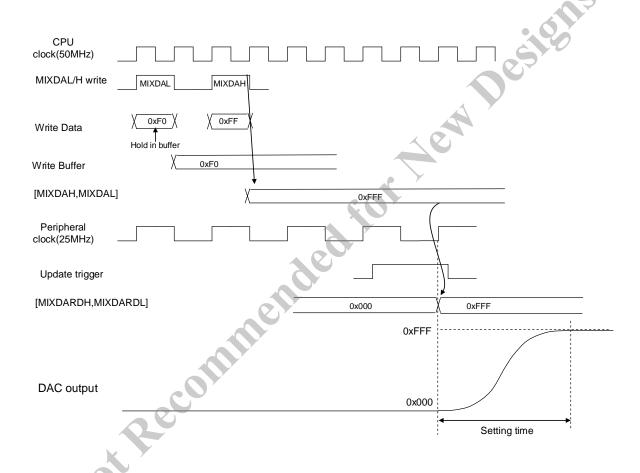

|     | 23.4 Oper     | ation                                                                        | 23-6         |

|     | 23.5 Limi     | tation of DAC                                                                | 23-6         |

|     | 23.5.1        | MIXDAL/H register access                                                     | 23-6         |

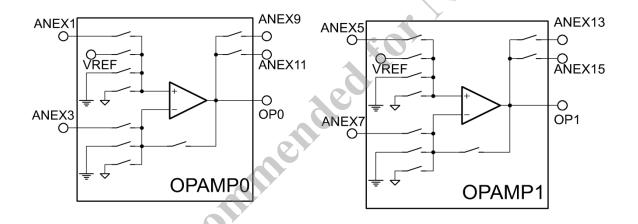

| 24. | _             |                                                                              |              |

|     |               | view                                                                         |              |

|     | Ū             | ster Description                                                             |              |

|     | 24.2.1        | Mix OPAMPn Configuration (MIXOPAn) (n=0-1)                                   | 24-2         |

|     | 24.2.2        | Mix OPAMPn PGA Configuration (MIXPGAn)(n=0-1)                                | 7            |

|     | 24.2.3        | Notice of OPAMP                                                              | 24-3         |

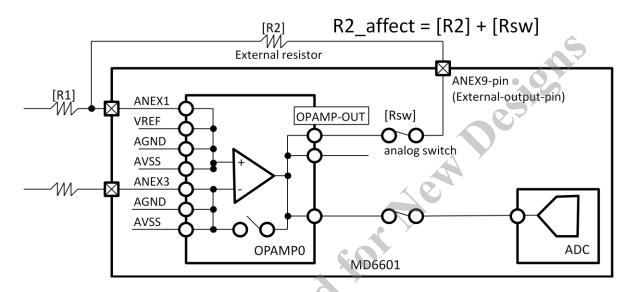

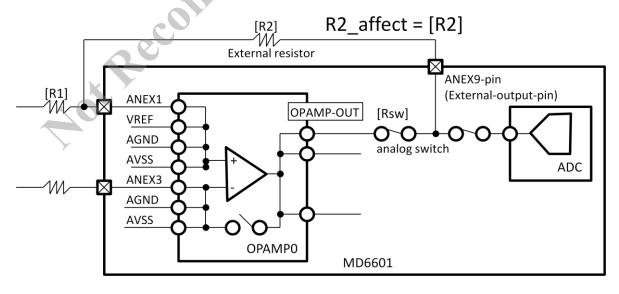

|     |               | .2.3.1. Resistance of analog switch that exists between OPAMP output and PIN |              |

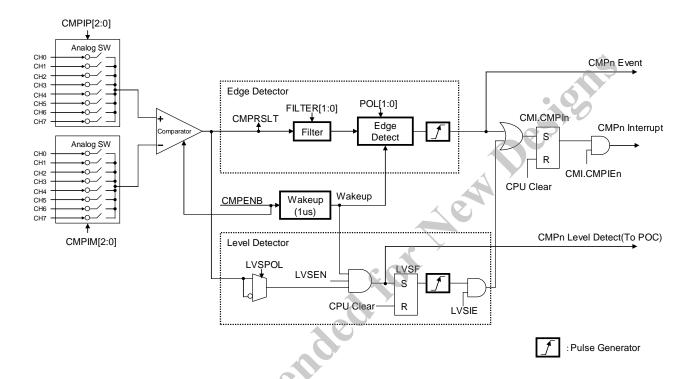

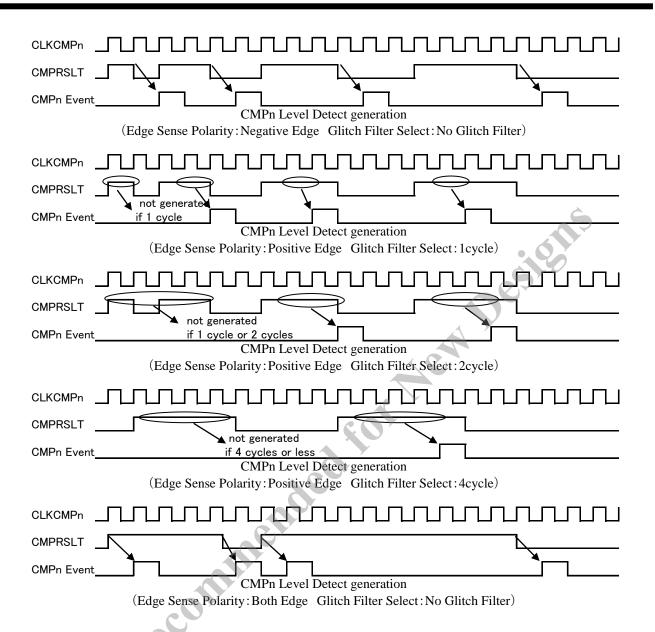

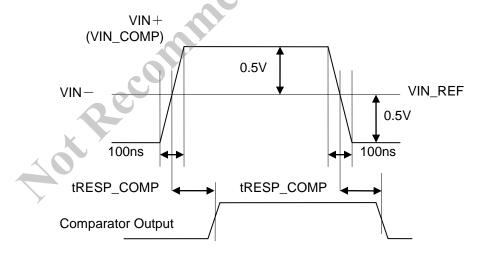

| 25. | Comparator    |                                                                              | 25-1         |

|     |               | view                                                                         |              |

|     | 25.2 Regi     | ster Description                                                             | 25-2         |

|     | 25.2.1        | Mix Comparator n Configuration (MIXCMPn) (n=0-3)                             | 25-3         |

|     |               | Mix Comparator n Functional Select (MIXCMSn) (n=0-3)                         |              |

|     | 25.2.3        | Comparator n Result (MIXCMRn) (n=0-3)                                        | 25-6         |

|     | 25.2.4        | Mix Comparator Interrupt(CMI)                                                | 25-7         |

|     | 25.3 Oper     | ration                                                                       | 25-8         |

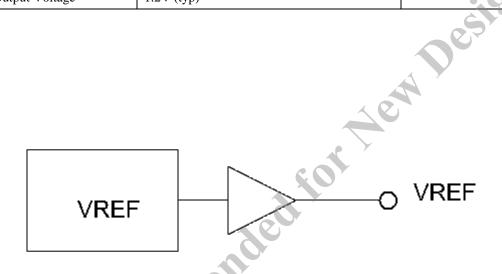

| 26. | Voltage Ref   | erence (VREF)view                                                            | 26-1         |

|     | 26.1 Over     | view                                                                         | 26-1         |

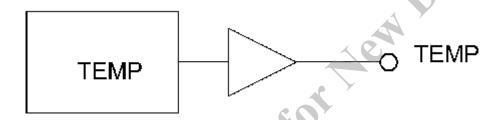

| 27  | Tamparatura   | e Sensor (TEMP)                                                              | 27 1         |

| 21. | 27.1 Over     | view                                                                         | 27-1<br>27-1 |

|     | 27.2 Regi     | viewster Description                                                         | 27-1         |

|     |               | Temperature sensor Control (TEMP)                                            |              |

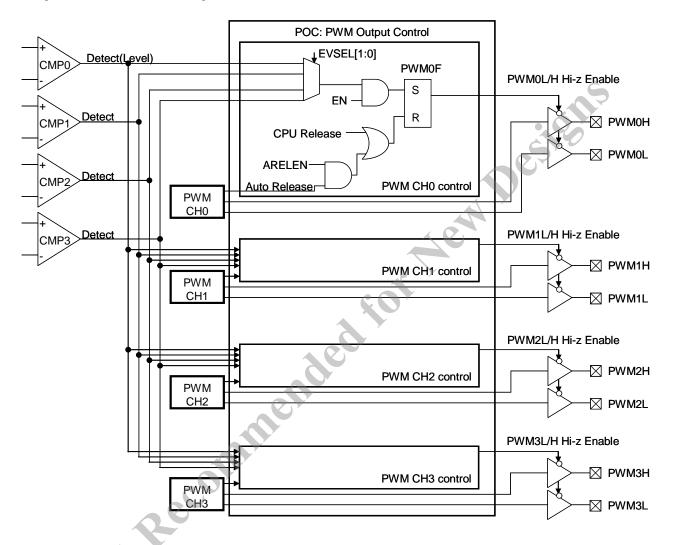

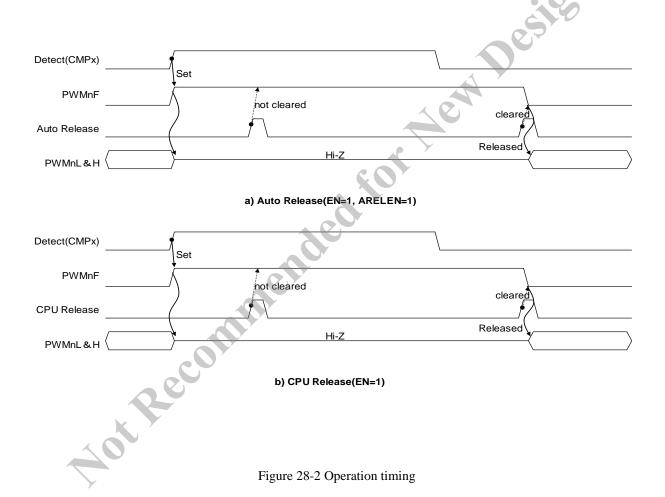

| 28. | POC (PWM      | Output Controller)                                                           | 28-1         |

|     |               | view                                                                         |              |

|     | 28.2 Regi     | ster Description                                                             | 28-2         |

|     | _             | POCCRn (POC Control Register)                                                |              |

|     | 28.2.2        | POCSTS (POC Status Register)                                                 | 28-3         |

|     | 28.3 Oper     | ation                                                                        | 28-4         |

| 29. | Electrical Cl | naracteristics                                                               | 29-1         |

| _,. |               | olute Maximum Ratings                                                        |              |

|     |               | ommended Operating Conditions                                                |              |

|     |               | age Information                                                              |              |

|     | 29.4 Curr     | ent Consumption                                                              | 29-2         |

|     |               | Voltage Detector                                                             |              |

|     |               | t Operation                                                                  |              |

|     |               | k Operation                                                                  |              |

|     |               | t ADC                                                                        |              |

|     |               | it ADC                                                                       |              |

|     | 29.10 12 bi   | t DAC                                                                        | 29-3         |

|     |               | MP                                                                           |              |

|     |               |                                                                              |              |

| 9.12 Comparator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 29-4                  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| 9.13 Voltage Reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 29-5                  |

| 9.14 Temperature Sensor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 29-5                  |

| 9.15 Analog GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 29-5                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                       |

| •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                       |

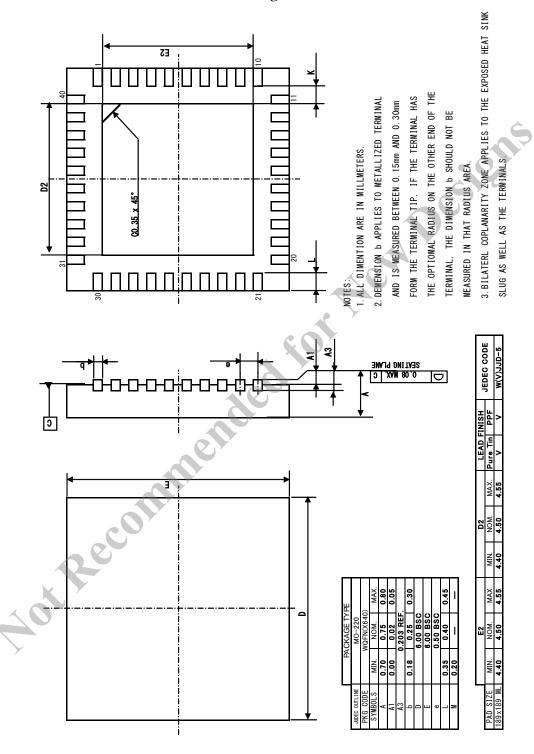

| 0.1 OFN40 PKG dimensional outline drawing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 30-1<br>30-1          |

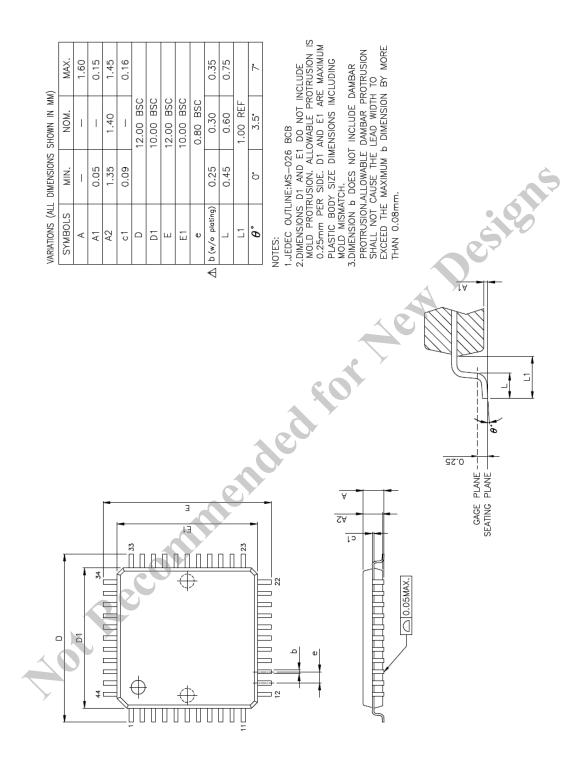

| 0.2 LOFP44 PKG dimensional outline drawing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 30-2                  |

| Ant Recommended for Aerical Recommendation of the Contract of |                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | .13 Voltage Reference |

### MD6601 (Mixed Signal MCU)

### 1. Product Overview

#### 1.1 Features

### 1.1.1 Analog Sub System

#### High Speed 10bit SAR ADC

- ➤ 2 Units (Independent)

- ➤ 10 Inputs/unit

- Conversion Speed: 4MSPS (4MSPS includes Sampling Time)

- > Simultaneous Sampling

- Sequence Conversion

- Configurable Conversion Triggers

- > Configurable Result Offset

### • High Precision 12bit SAR ADC

- ➤ 1 Unit

- ➤ 10 inputs

- ➤ Conversion Speed: 1MSPS

- Sequence Conversion

- ➤ Configurable Conversion Triggers

- Configurable Result Offset

### • High Precision 12bit DAC

- ➤ 1 Units

- Update Rate: 1MSPS

- ➤ Configurable Update Triggers

#### High Speed Analog Comparator

- > 4 Units

- Response Time: 20ns

- ➤ Rail-to-Rail Input

- Digital Hazard Filter

- Configurable Event Generation

#### Operational Amplifier (OPAMP)

- ➤ 2 Units

- ➤ Rail-to-Rail Input / Output

- > Standalone or Unity, Selectable

#### Voltage Reference

➤ Generate 1.2V

### • Temperature Sensor

- Measures Junction Temparature

- Read from Internal ADC

#### Analog Inter-Connection Network

Configurable Inter-Connections among In/Out Signals of Analog Modules and External Pins

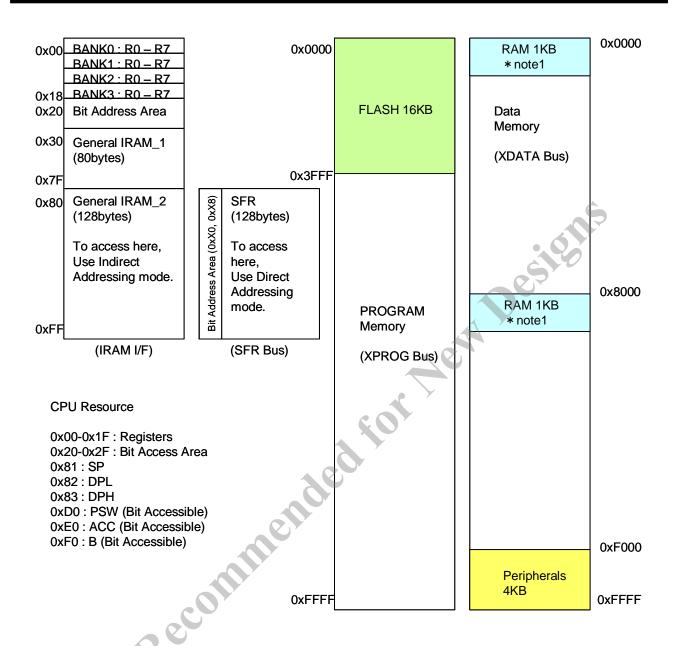

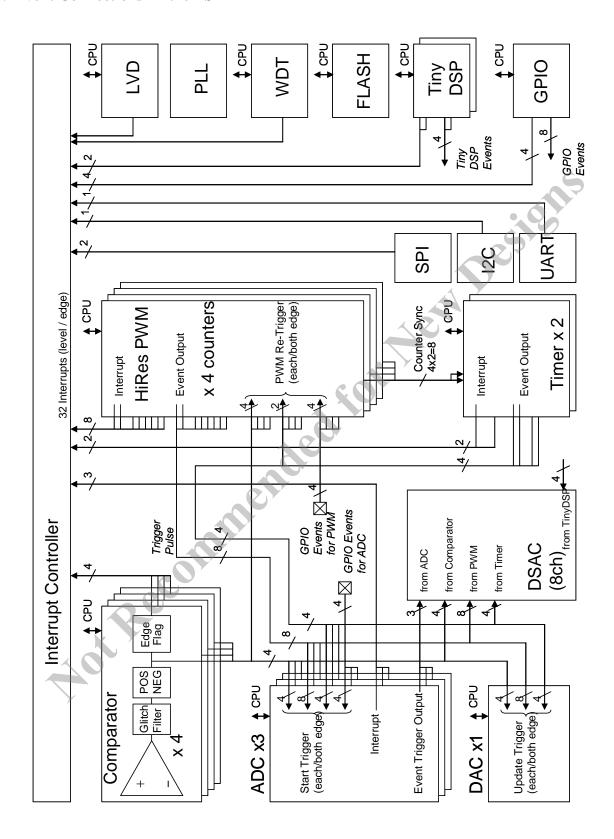

### 1.1.2 Digital Sub System

#### Pipelined 8bit CPU

- ➤ 8051 Compatible Instructions

- ➤ Pipeline with 3-5 stages

- ➤ 50MHz, 1cycle/8bit-instruction

- 256bytes Internal RAM

### • 1-wire On-Chip-Debug Interface

- ➤ R/W to all Internal Resources

- ➤ Go / Step / Stop

- PC Break / Data Access Break

- > Reset

- FLASH Program / Erase

#### FLASH Memory

- ➤ 16KB

- > Feeds 8bit Instruction in 1cyc

- Protection Supported

#### Internal RAM

> 1KB

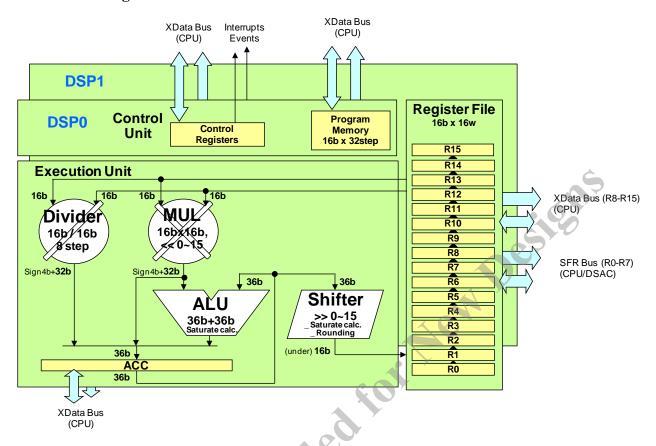

#### Tiny DSP

- 2 Units (Independent)

- 16bit Fixed Point

- > Sequence Programmable

- ➤ 32step Instruction Memory

- ► 16 Data Registers + Accumulator

- ➤ Instructions: Multiply, Division, MAC, Barrel-Shift, Move, Jump

- ➤ Hardware Divider Supported

- Event Synchronized Sequence

- Configurable Event Generation

- ➤ Example: 2P3Z IIR Filter→10 cyc

#### High Resolution PWM

- > 8-outputs (4-pairs for Hi/Lo Sides)

- ➤ 4 x 16bit Counters for each pair

- ➤ Counters can be Synchronized

- > PWM Resolution: 1ns

- ➤ Configurable PWM Duty (0%-100%) and Carrier Frequency in every PWM cycle

- Configurable Non-Overlap Time

- ➤ Counter Modes: Up and Up/Down

- Phase Shift Mode Supported

- ➤ Re-Trigger Operations by Internal /external Events

#### Direct SFR Access Controller

- Direct Data Transfer between Peripheral Registers (SFR: Special Function Register)

- > Selectable Transfer Trigger Event

### Interrupt Timers

- ➤ 2 Units

- ➤ 16bit Counter

- Compare Match generates Event

- > synchronization with PWM

### SPI

- ➤ 1 Unit, Master/Slave

- > 3-wires (Clock, MOSI, MISO)

- Dedicated Baud Rate Generator

### • I2C (SMBUS)

- ➤ 1 Unit, Master/Slave

- Dedicated Baud Rate Generator

- ➤ SMBUS Compatible I/O Buffer

#### UART

- ➤ 1 Unit

- Dedicated Baud Rate Generator

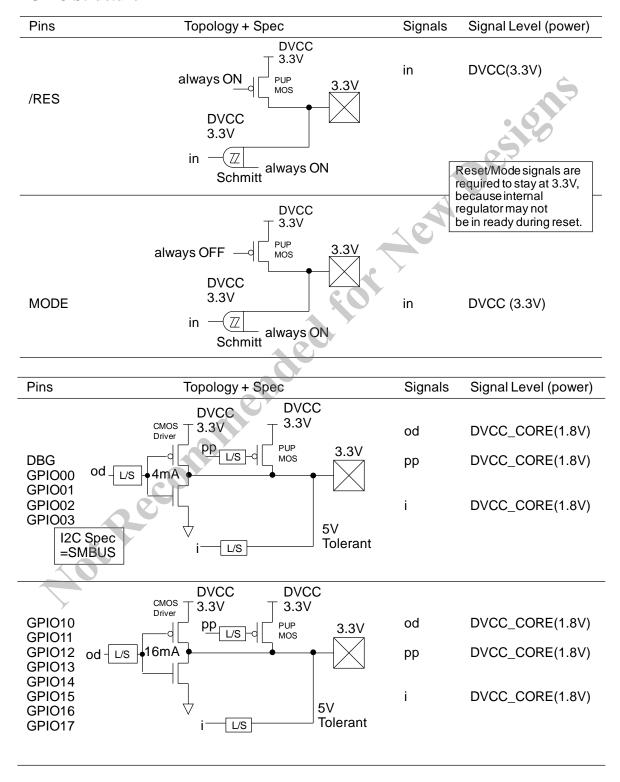

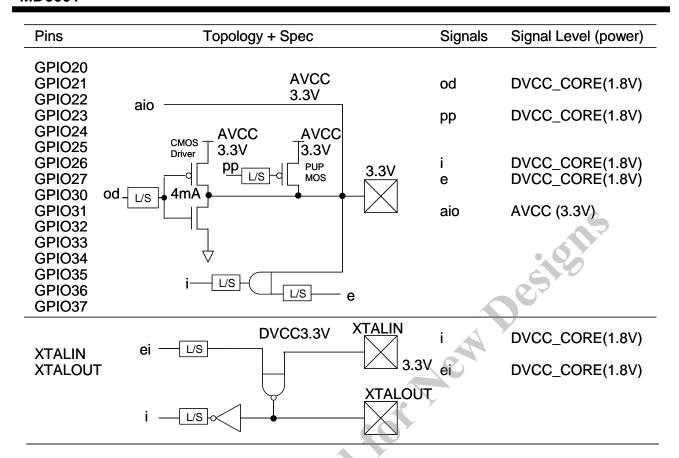

#### GPIO

- ➤ Digital & Analog Multiplexed

- ➤ Pull-Up MOS

- +(1)

Agt Reconning ➤ Configurable as Interrupt Sources

### • Interrupt Controller

- Watch Dog Timer (WDT)

- Low Voltage Detector (LVD)

### **Reset Control**

- External Reset

- ➤ Internal Power On Reset (POR)

#### Clock Control

- External XTAL Oscillator

- ➤ Internal Ring Oscillator (IRC)

- > PLL

### • External Power Supply Voltage

- ➤ 3.3V for each DVCC and AVCC

- ➤ Internal Core Voltage Regulator

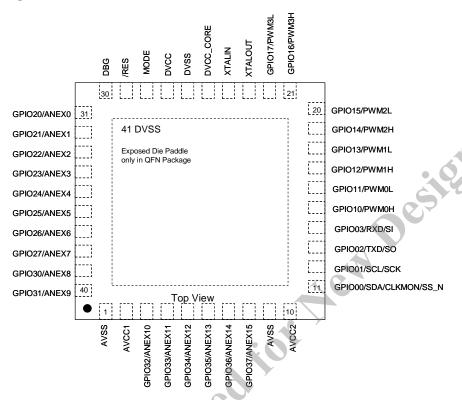

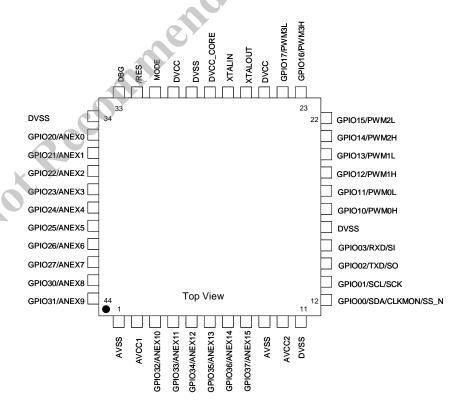

### **Package**

- QFN-40 (6x6mm, P0.5)

- LQFP-44 (10x10mm, P0.8)

### 1.2 Description

The LSI is a MCU (Micro Controller Unit) with Rich and Powerful Analog Elements such as High Speed 10bit ADC, High Precision 12bit ADC/DAC, High Speed Comparators, and Operational Amplifiers. These analog blocks can be connected via inter-connection-network to configure the LSI as a user-defined mixed signal device. Moreover, this LSI integrates not only CPU but also Dedicated Tiny DSP separated from CPU, High-Resolution PWM, and Automatic Data Transfer Scheme in one chip, which realize Self-Running Feedback Control System without CPU. In such system, CPU can engage in other tasks such as intelligent controls, communications, system watches, error detections and non-linear controls, etc. and then, the LSI will provide you high performance control system

## 1.3 Application

- Digital DC-DC Power Supply

- Digital AC-DC Power Supply

- Digital Assist Power Supply

- LED Lighting Control

- LED Signage

- Wireless Charger

- MPPT Solar Controller

- Inverter for Solar Battery

- Inverter for Motor Control

- E-Bike, E-Assist Bicycle

- EV Charger

- D ...

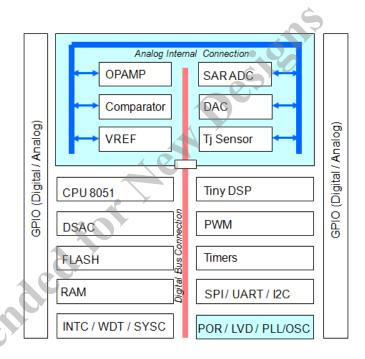

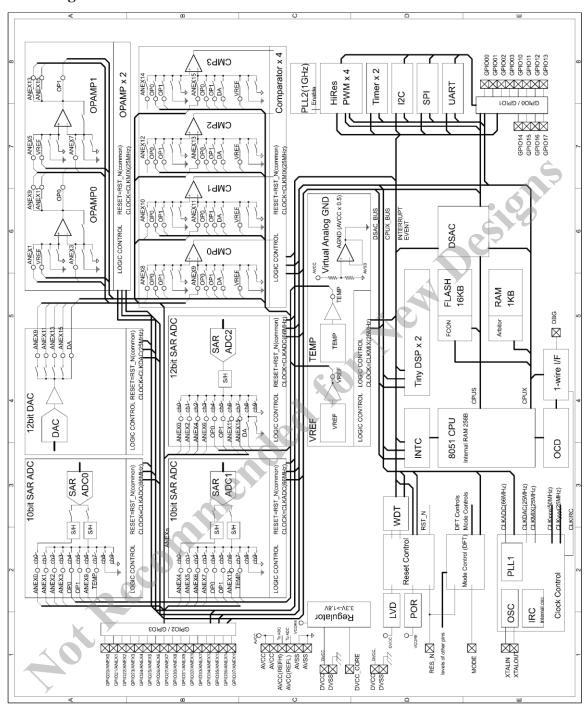

Figure 1-1 MSM Internal Functions

### 1.4 Ordering Information

| Part #     | FLASH/RAM | Vcc  | Package | Note        |

|------------|-----------|------|---------|-------------|

| MD6601FNV  | 16KB/1KB  | 3.3V | QFN-40  | Tray        |

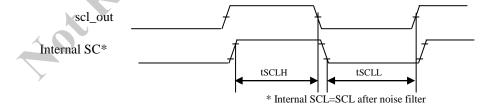

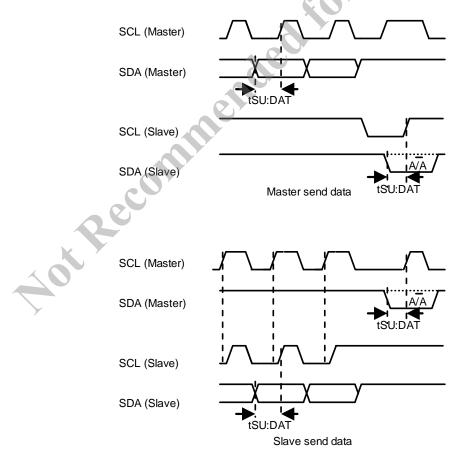

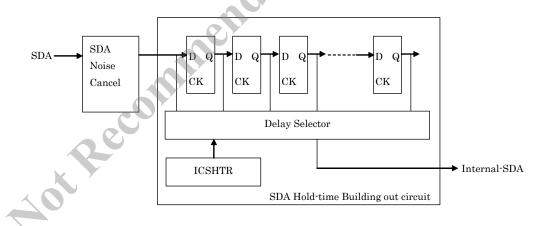

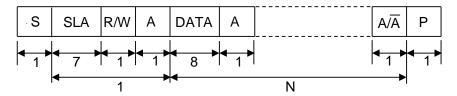

| MD6601FNVL | 16KB/1KB  | 3.3V | QFN-40  | Tape & Reel |